НИУ МЭИ

Кафедра ВМСиС

# **Вычислительные системы**

**Конспект лекций**

Лектор к.т.н. проф. И. И. Ладыгин

## СОДЕРЖАНИЕ

|                                                                                            |     |

|--------------------------------------------------------------------------------------------|-----|

| Лекция 1.....                                                                              | 4   |

| 1. Основные понятия в области вычислительных систем .....                                  | 4   |

| 1.1 Введение. Основные определения.....                                                    | 4   |

| Лекция 2.....                                                                              | 10  |

| 1.2 Понятие Фон-неймановской архитектуры.....                                              | 10  |

| 1.3 Парадигмы Фон-неймановской архитектуры.....                                            | 12  |

| 1.4 Особенности Фон-неймановской архитектуры.....                                          | 12  |

| Лекция 3.....                                                                              | 16  |

| 2. Эволюция способов обработки данных .....                                                | 16  |

| Лекция 4.....                                                                              | 24  |

| 3. Уровни параллелизма при выполнении прикладных задач .....                               | 24  |

| 4. Распараллеливание последовательных частей программ.....                                 | 28  |

| Лекция 5.....                                                                              | 33  |

| 5. Оценка производительности ВС .....                                                      | 33  |

| Лекция 6.....                                                                              | 37  |

| 6. Методы оценки производительности ВС.....                                                | 37  |

| 7. Система тестов SPEC. Единицы измерения производительности ВС .....                      | 39  |

| Лекция 7.....                                                                              | 45  |

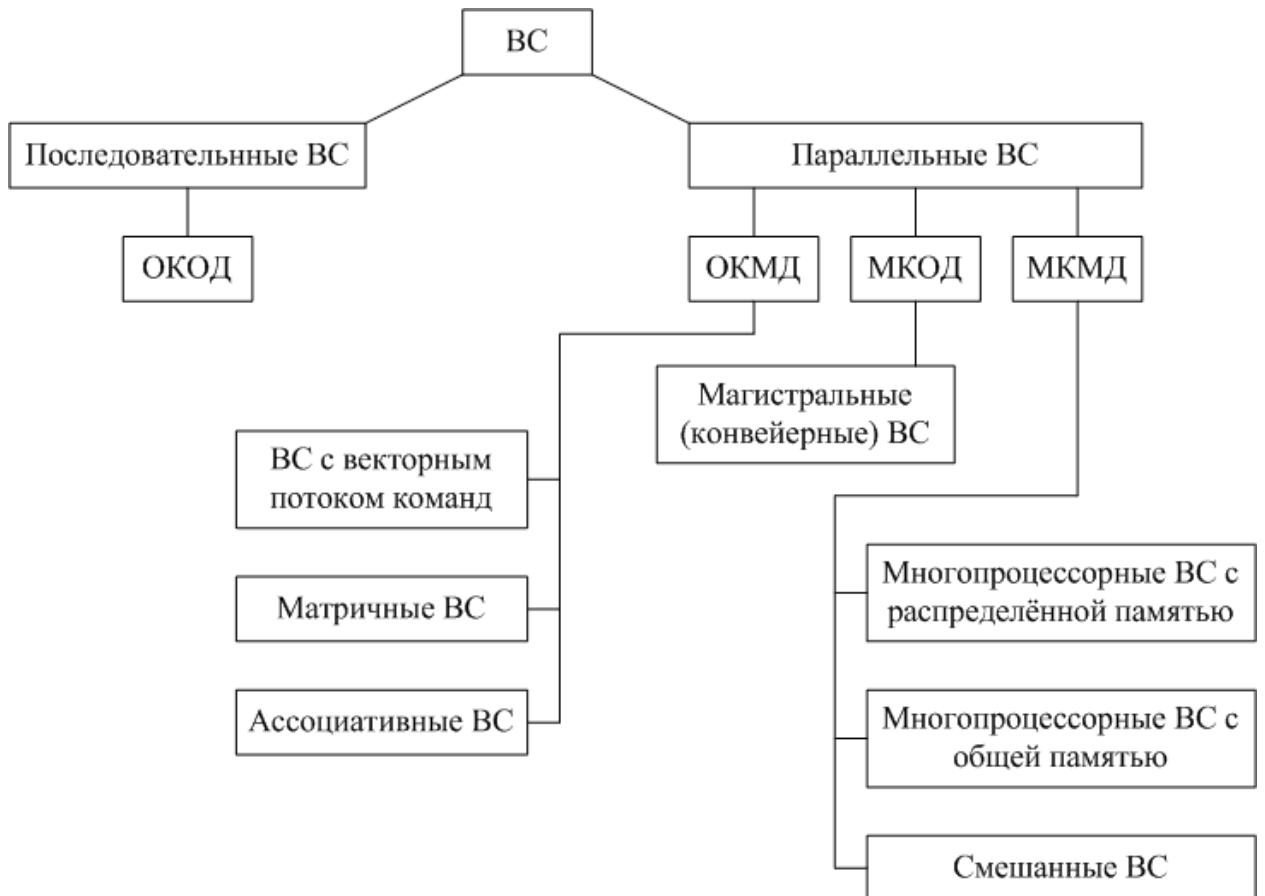

| 8. Классификация вычислительных систем .....                                               | 45  |

| 9. Режимы обработки данных ВС .....                                                        | 57  |

| 9.1 Пакетный режим функционирования ВС .....                                               | 57  |

| 9.2 Режим разделения времени (потоковый режим).....                                        | 58  |

| 9.3 ВС реального времени .....                                                             | 61  |

| Лекция 8.....                                                                              | 63  |

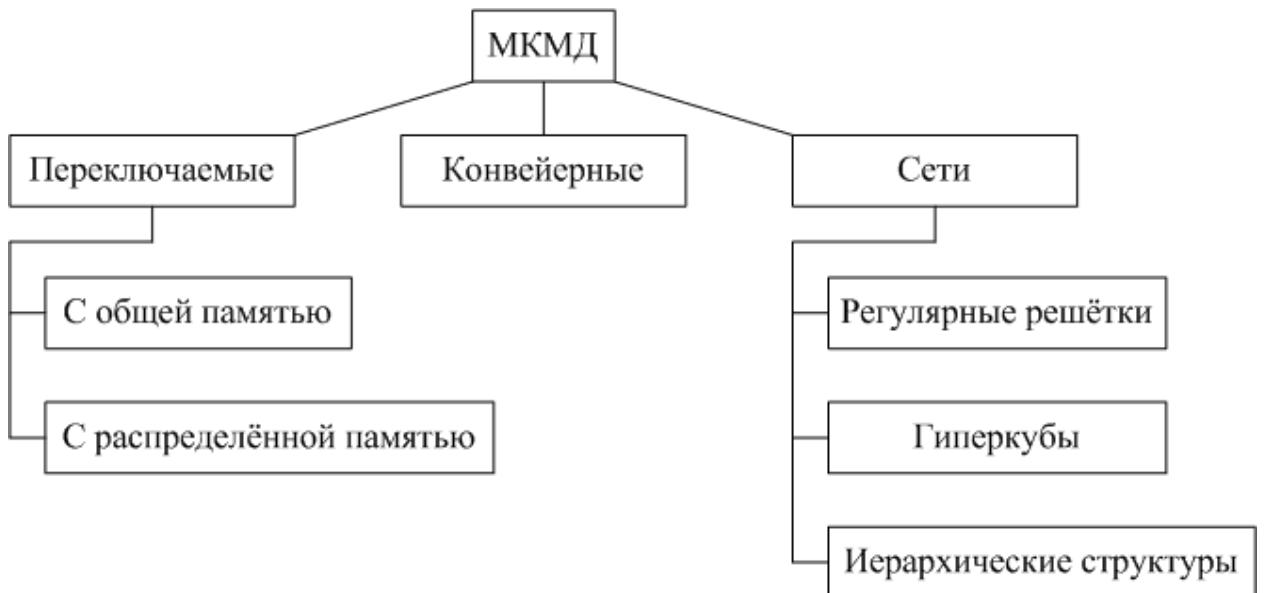

| 10. Системы класса MIMD (МКМД).....                                                        | 63  |

| 11. ВС с общей памятью (UMA) .....                                                         | 65  |

| 12. Проблема когерентности в ВС с общей памятью.....                                       | 66  |

| Лекция 9.....                                                                              | 68  |

| 13. ВС с распределенной памятью .....                                                      | 68  |

| Лекция 10.....                                                                             | 70  |

| 14. Постановка задачи назначения .....                                                     | 70  |

| 14.1 Модели представления задач .....                                                      | 71  |

| 14.2 Алгоритм поиска критического пути графа.....                                          | 73  |

| 14.3 Применение стратегий назначения при решении задачи назначения.....                    | 76  |

| Лекция 11.....                                                                             | 77  |

| 14.4 Обеспечение надежности вычислений .....                                               | 77  |

| 14.5 Многозадачный режим функционирования Многопроцессорной<br>Вычислительной Системы..... | 79  |

| Лекция 12.....                                                                             | 82  |

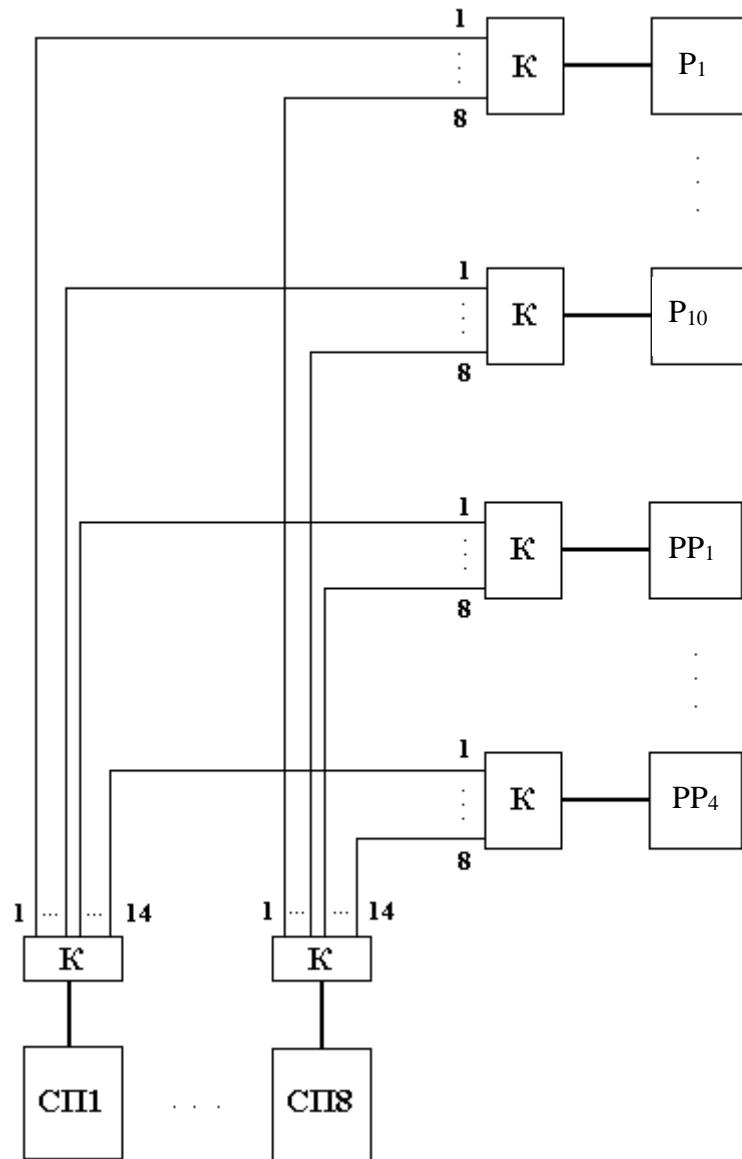

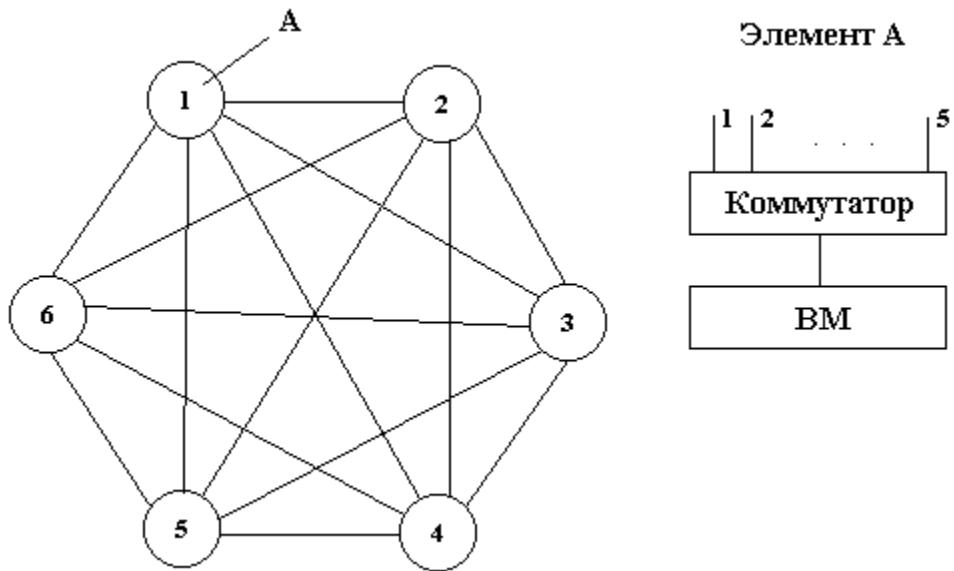

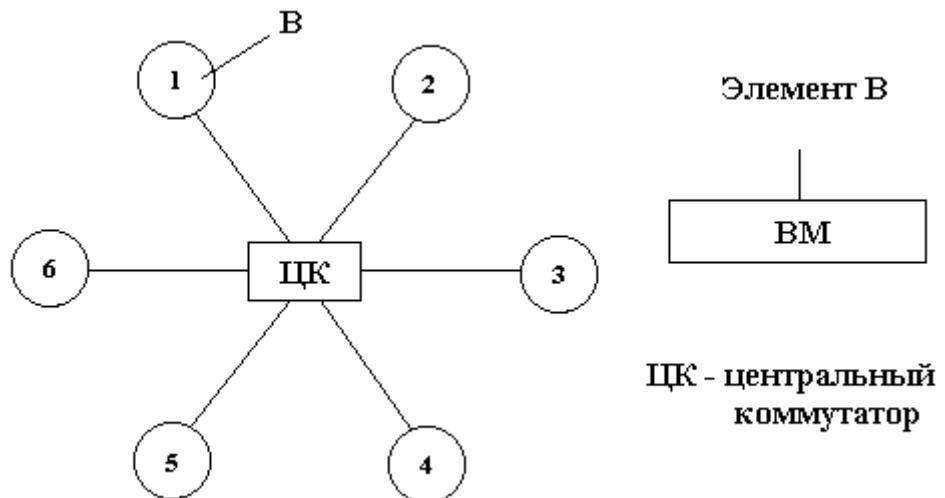

| 15. Системы коммутации .....                                                               | 82  |

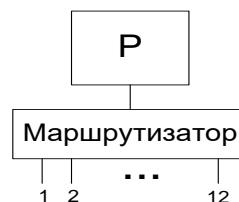

| 15.1 Шинные структуры .....                                                                | 83  |

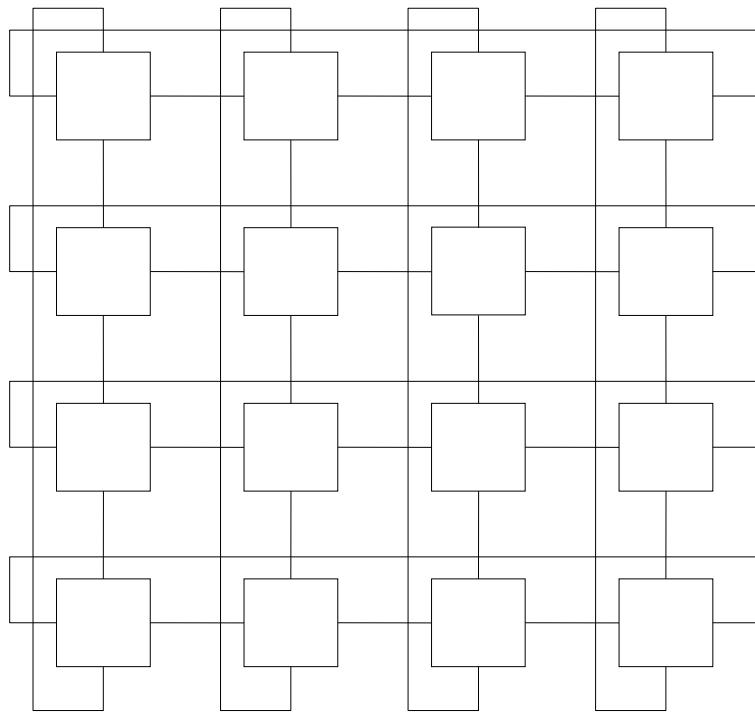

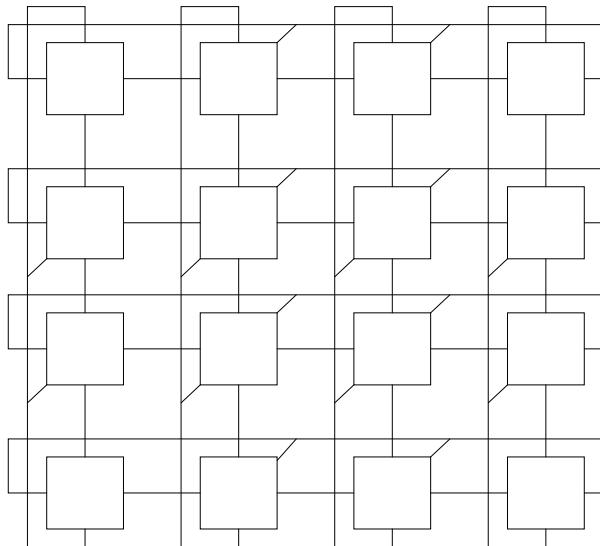

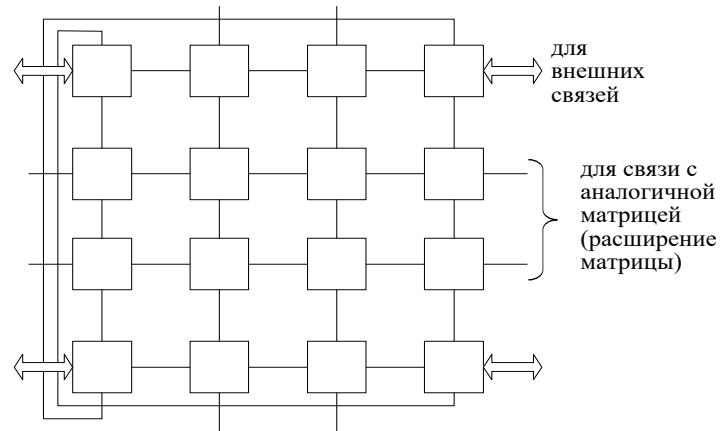

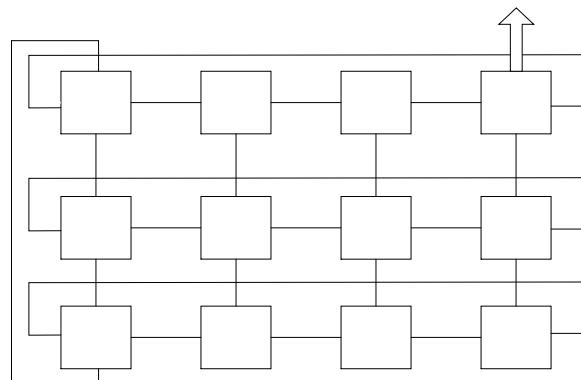

| 15.2 Матричные структуры .....                                                             | 89  |

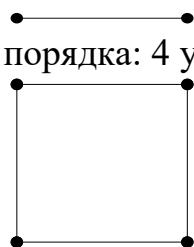

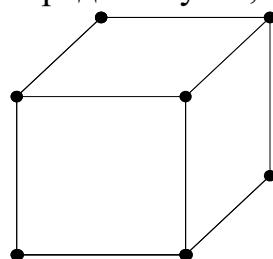

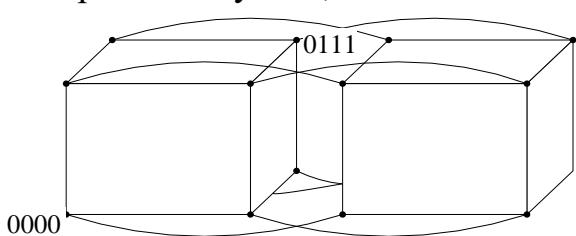

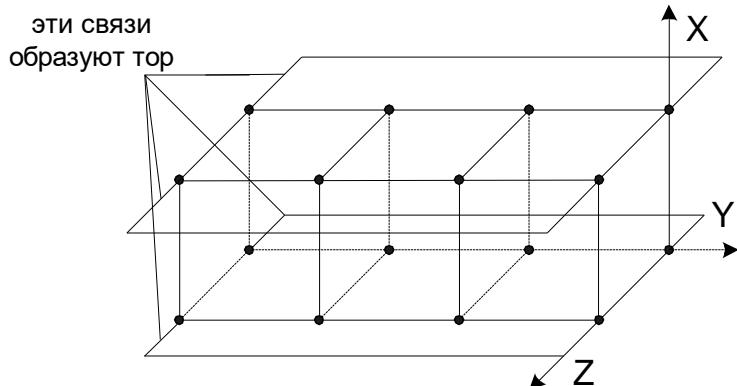

| 15.3 Кубические структуры .....                                                            | 92  |

| Лекция 13.....                                                                             | 96  |

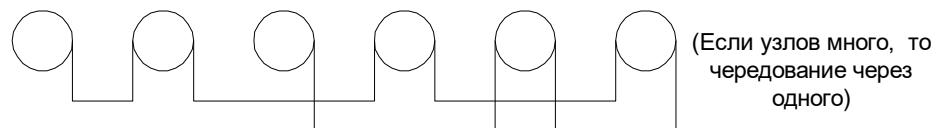

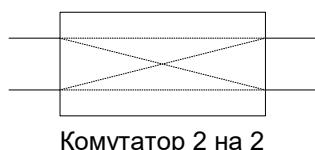

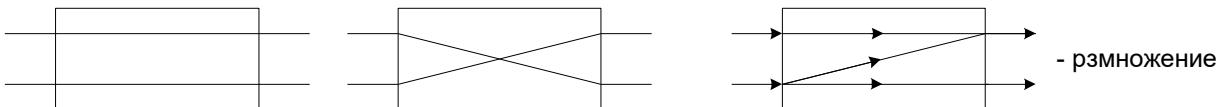

| 15.4 Многоступенчатые коммутаторы .....                                                    | 96  |

| 15.5 Сеть Омега - Коммутатор Omega ILLIAC-IV .....                                         | 97  |

| 15.6 Коммутационная сеть flip (сеть перестановок) .....                                    | 98  |

| Лекция 14.....                                                                             | 100 |

| 16. ВС на основе векторных процессоров .....                                               | 100 |

| Лекция 15.....                                                                             | 105 |

|                |                                                                          |     |

|----------------|--------------------------------------------------------------------------|-----|

| 17.            | ВС класса ОКМД на основе матричных процессоров .....                     | 105 |

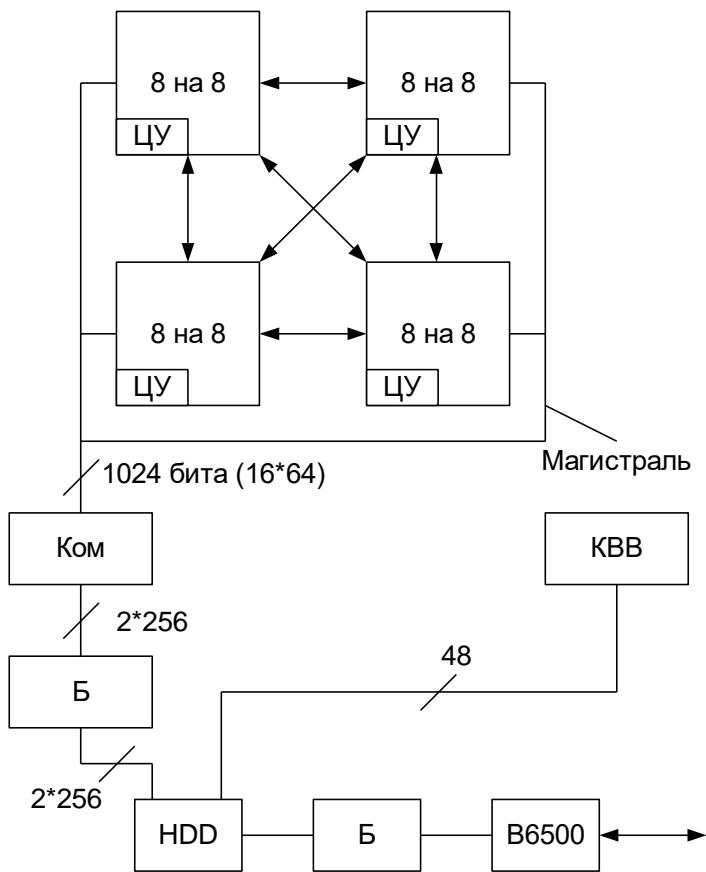

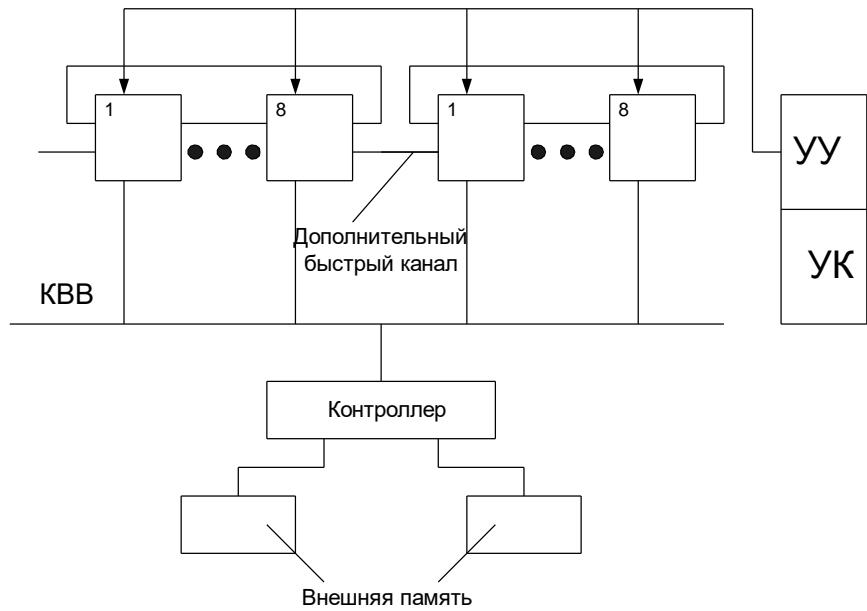

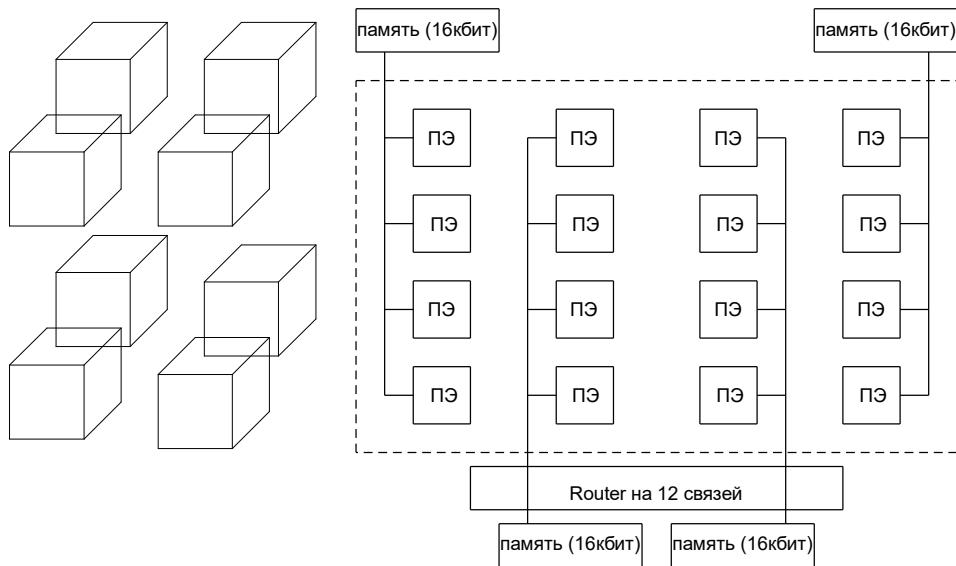

| 17.1           | Структурная схема ILLIAC- IV .....                                       | 107 |

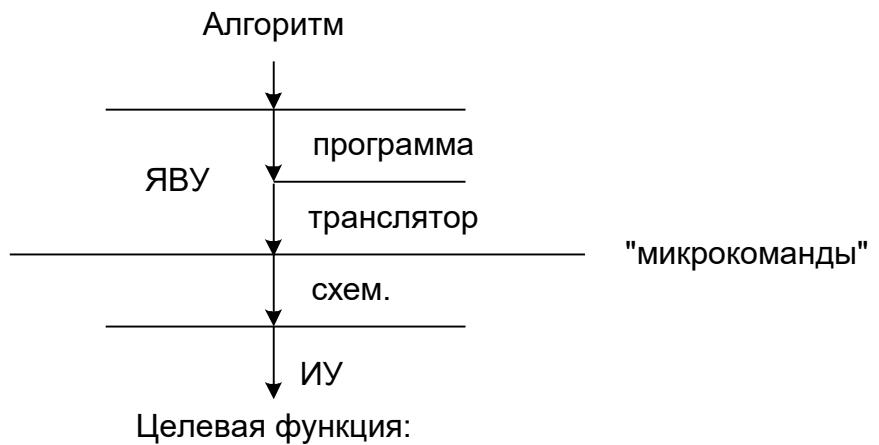

| 17.2           | Нисходящее проектирование матричных процессоров .....                    | 110 |

| 17.3           | Оценка эффективности ВС на основе матричных процессоров .....            | 115 |

| Лекция 16..... |                                                                          | 118 |

| 18.            | Супер-ЭВМ семейства CRAY (ВС с ОП).....                                  | 118 |

| 18.1           | CRAY C-90.....                                                           | 122 |

| 18.2           | СуперЭВМ NEC SX (1÷6).....                                               | 124 |

| Лекция 17..... |                                                                          | 128 |

| 19.            | ВС на основе ассоциативных процессоров .....                             | 128 |

| 19.1           | Введение .....                                                           | 128 |

| 19.2           | Ассоциативные процессоры .....                                           | 131 |

| 19.3           | Ассоциативные процессоры с пословной организацией .....                  | 132 |

| 19.3.1         | Базовая структура .....                                                  | 132 |

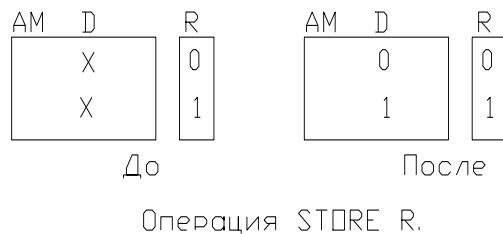

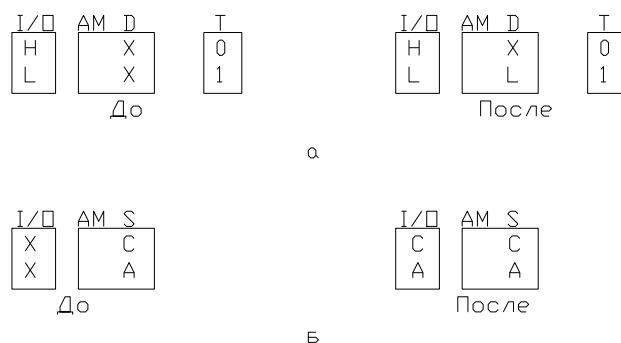

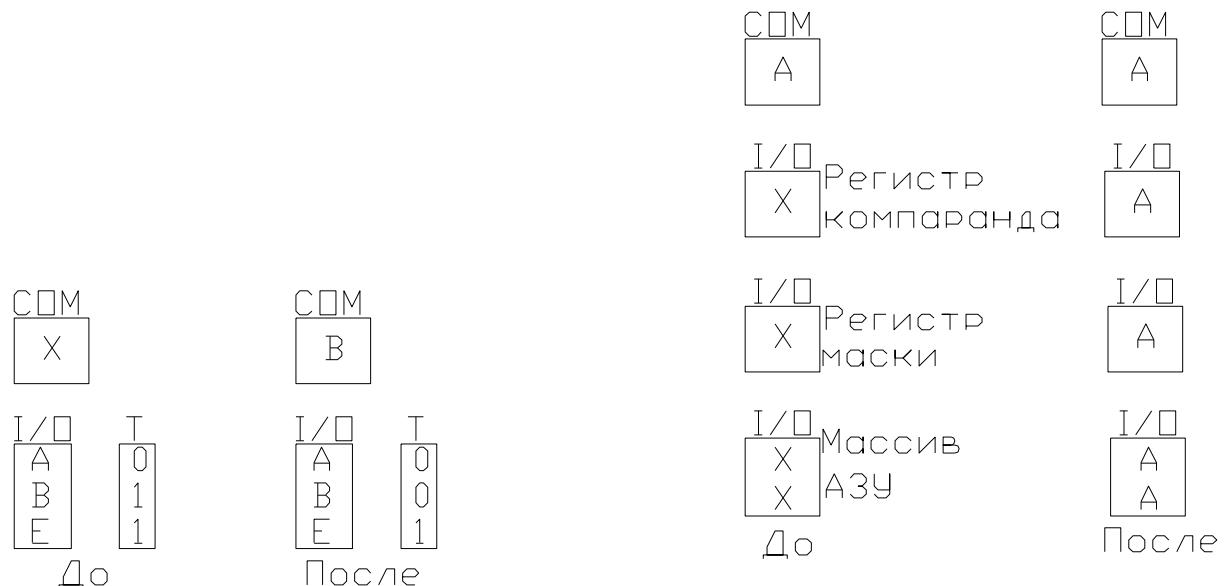

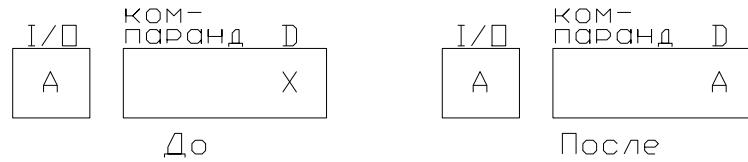

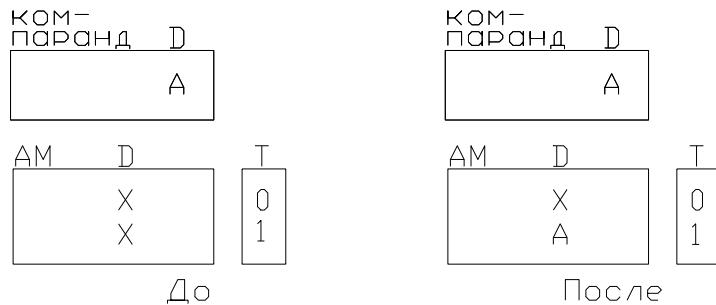

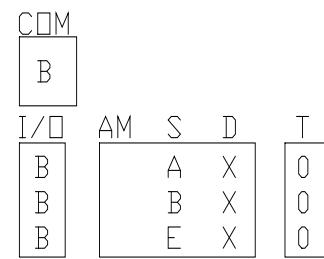

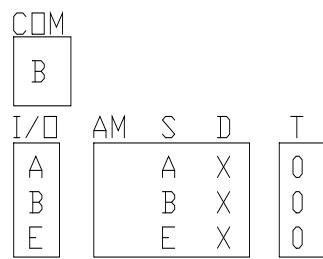

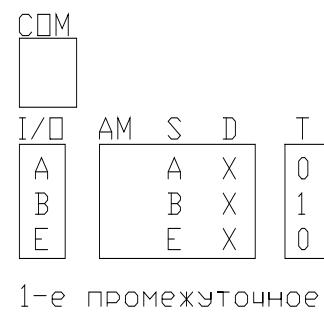

| 19.3.2         | Базовые операции .....                                                   | 137 |

| 19.4           | Ассоциативный процессор Staran .....                                     | 144 |

| Лекция 18..... |                                                                          | 148 |

| 20.            | Особенности программного обеспечения параллельных систем .....           | 148 |

| 20.1           | Языки параллельного программирования.....                                | 150 |

| 20.2           | Особенности трансляторов параллельных систем .....                       | 154 |

| 20.3           | Операционные системы .....                                               | 155 |

| Лекция 19..... |                                                                          | 157 |

| 21.            | Процессоры высокопроизводительных вычислительных систем .....            | 157 |

| 22.            | Предшественники многоядерных процессоров .....                           | 159 |

| 22.1           | Особенности построения Elbrus 3M .....                                   | 161 |

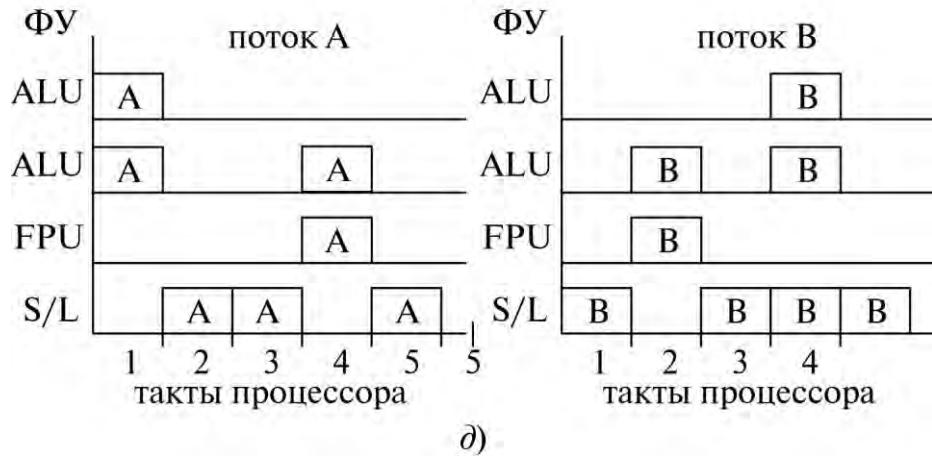

| 22.2           | Технология Hyper Threading .....                                         | 164 |

| 22.3           | Оценка эффективности двухядерного процессора.....                        | 171 |

| Лекция 20..... |                                                                          | 174 |

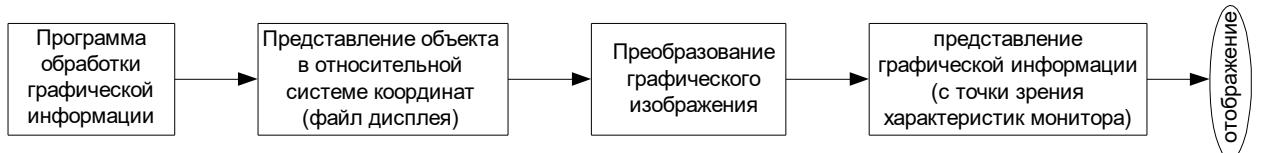

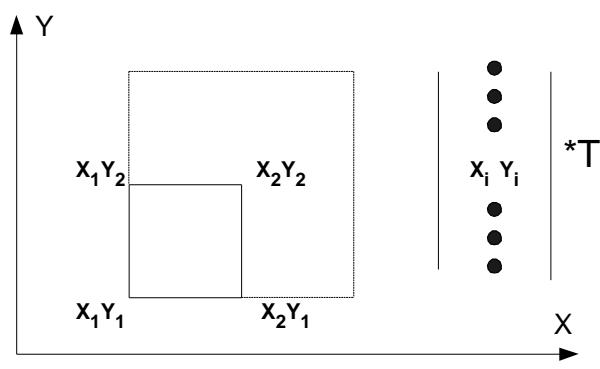

| 23.            | Основы обработки графической информации .....                            | 174 |

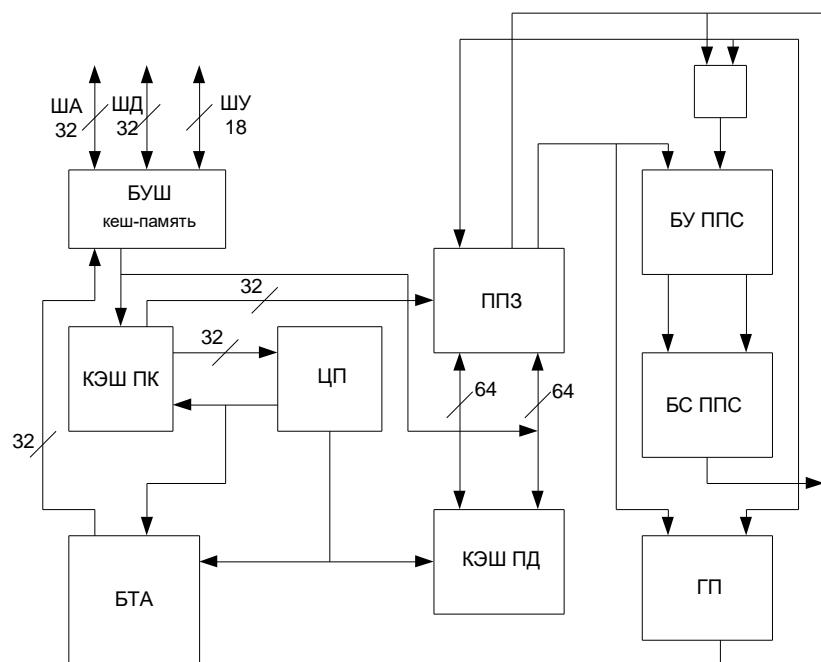

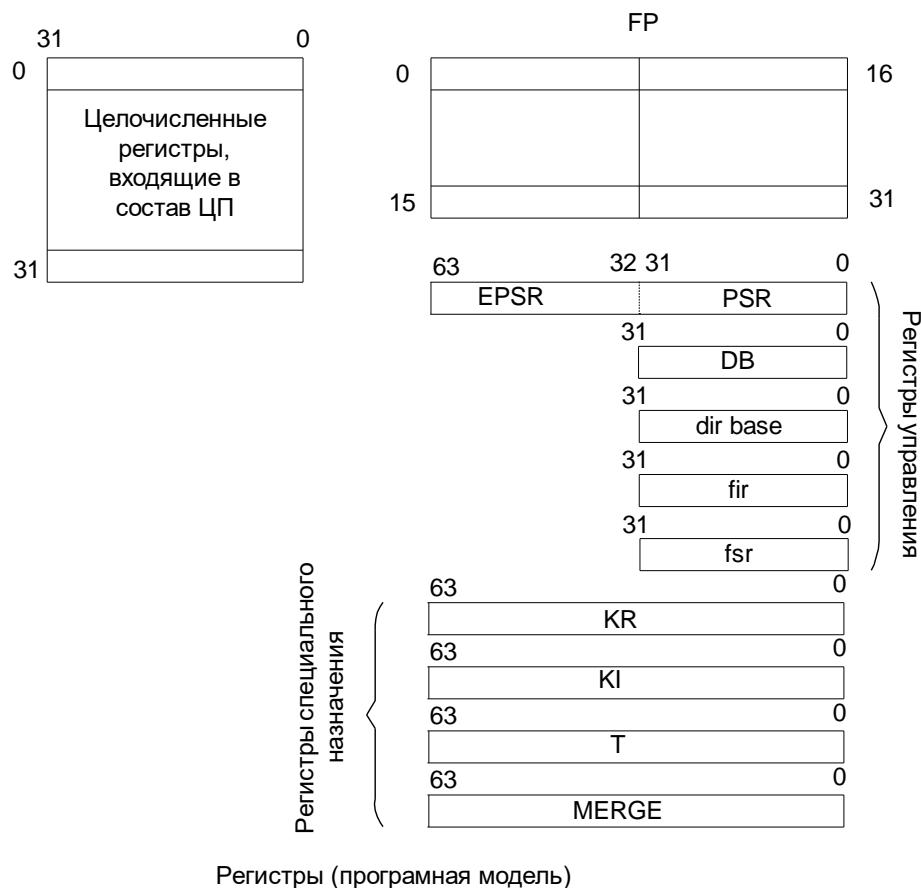

| 23.1           | Процессор i860. Структурная схема. Регистры .....                        | 176 |

| Лекция 21..... |                                                                          | 181 |

| 24.            | Вычислительная система «ЭЛЬБРУС».....                                    | 181 |

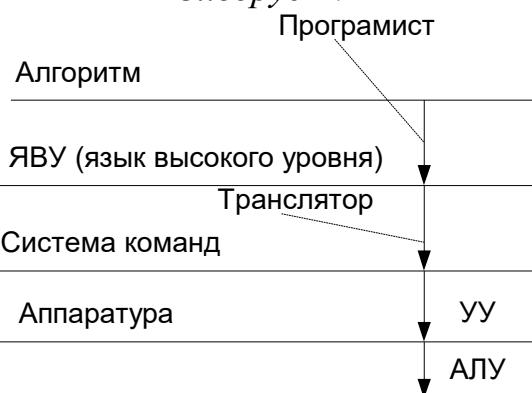

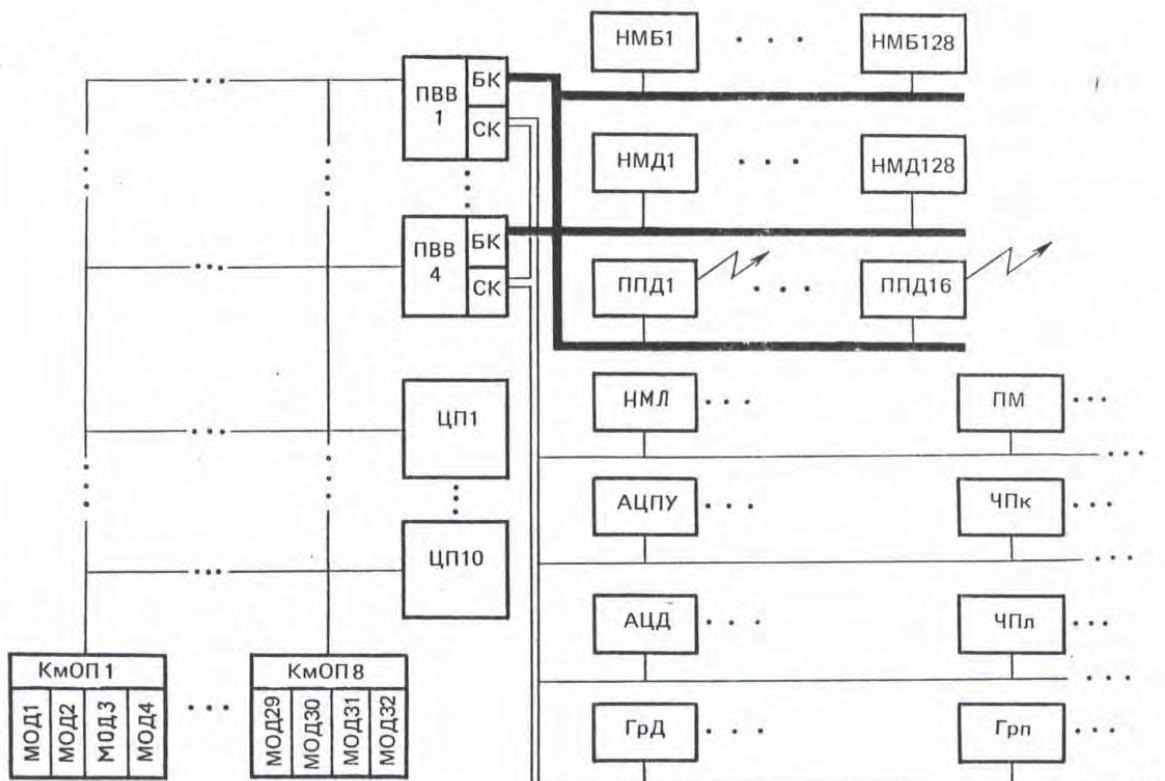

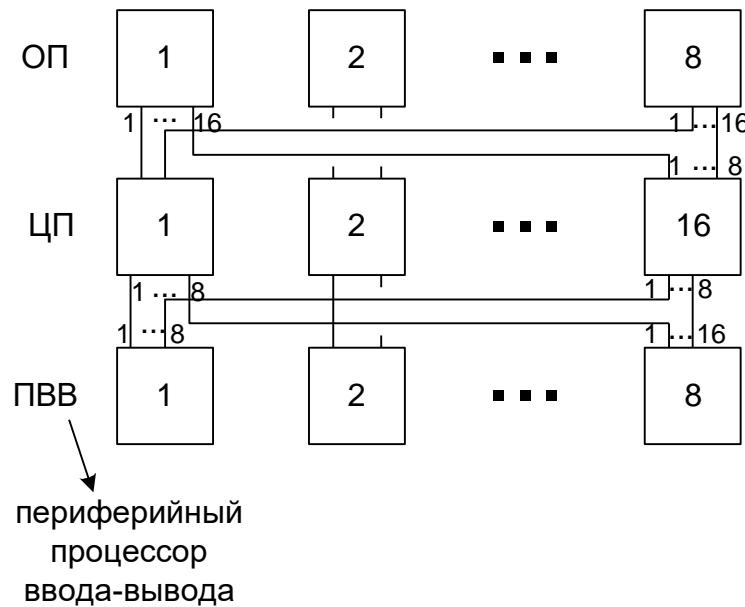

| 24.1           | Мультипроцессорный вычислительный комплекс «ЭЛЬБРУС-2» (МКМД с ОП) ..... | 184 |

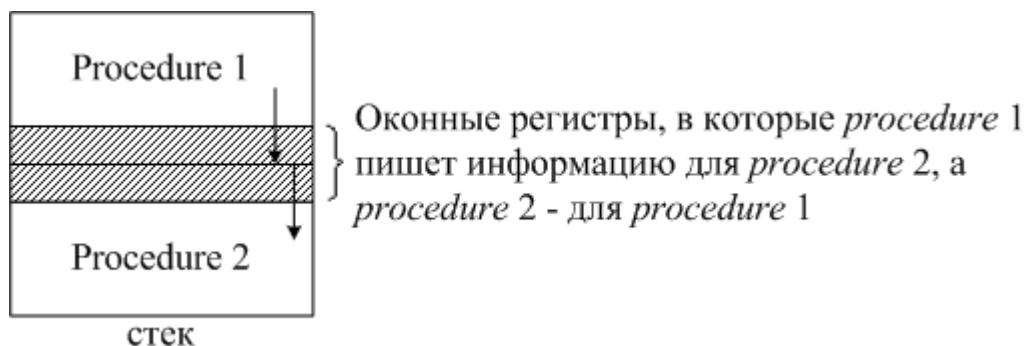

| 24.1.1         | Центральный процессор .....                                              | 185 |

| 24.1.2         | Формат данных ЦП .....                                                   | 188 |

| 24.1.3         | Организация оперативной памяти .....                                     | 190 |

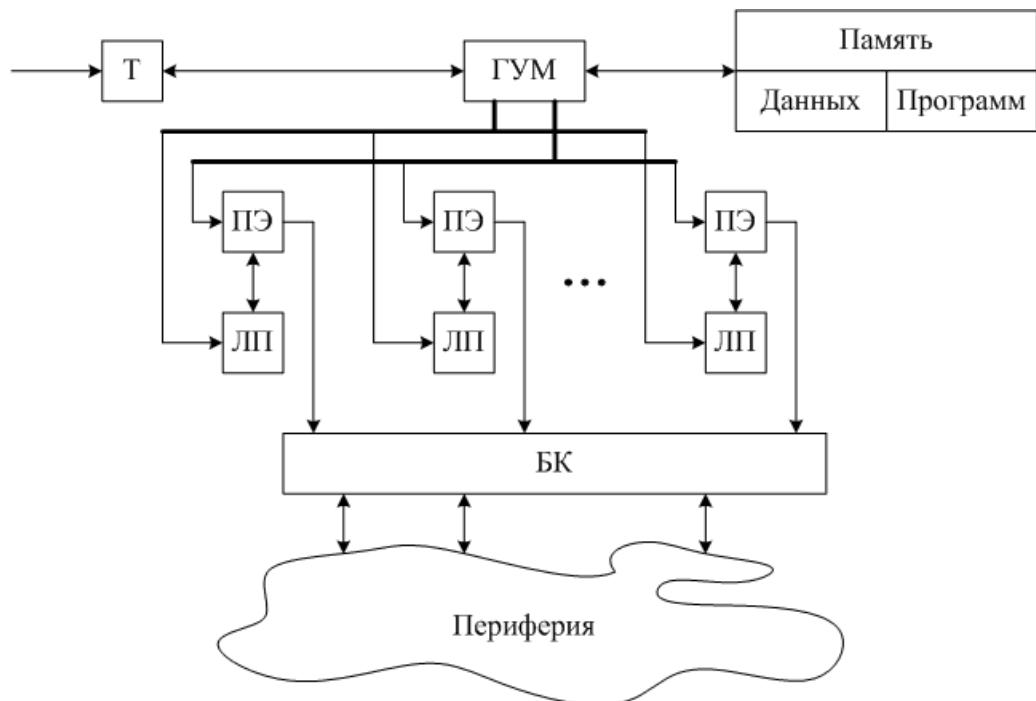

| 24.2           | МВС «Эльбрус-3» (МКМД с ОП) .....                                        | 191 |

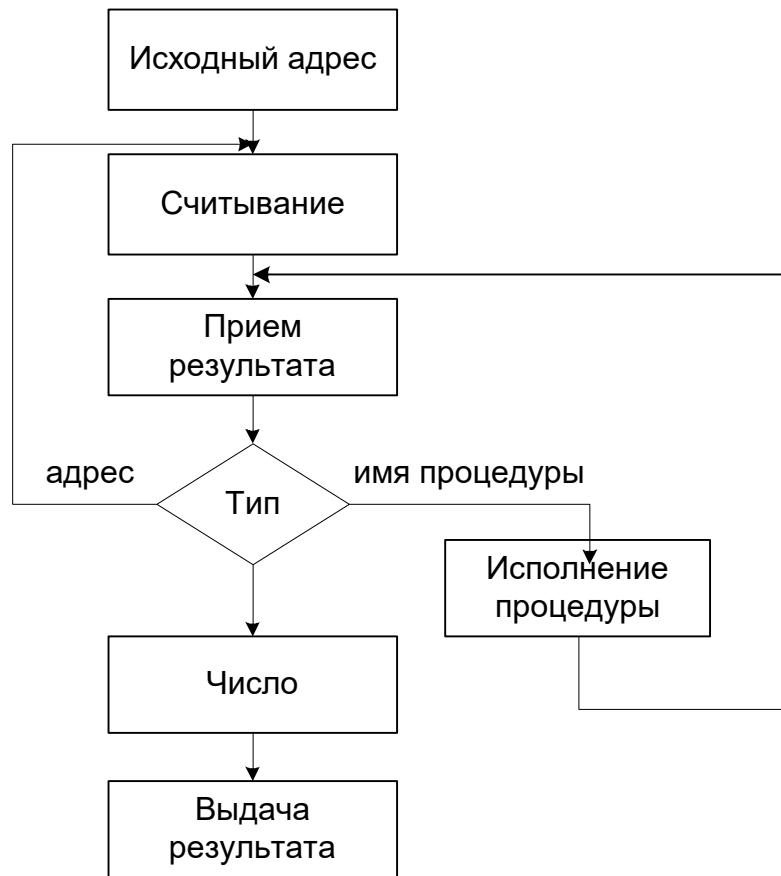

| 24.2.1         | Основные принципы обработки данных в «Эльбрус-3».....                    | 193 |

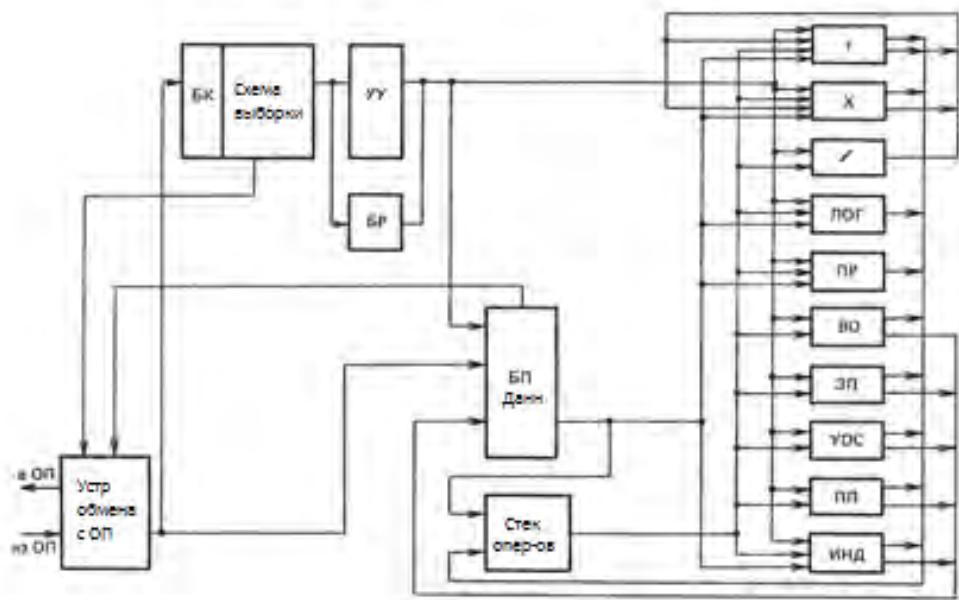

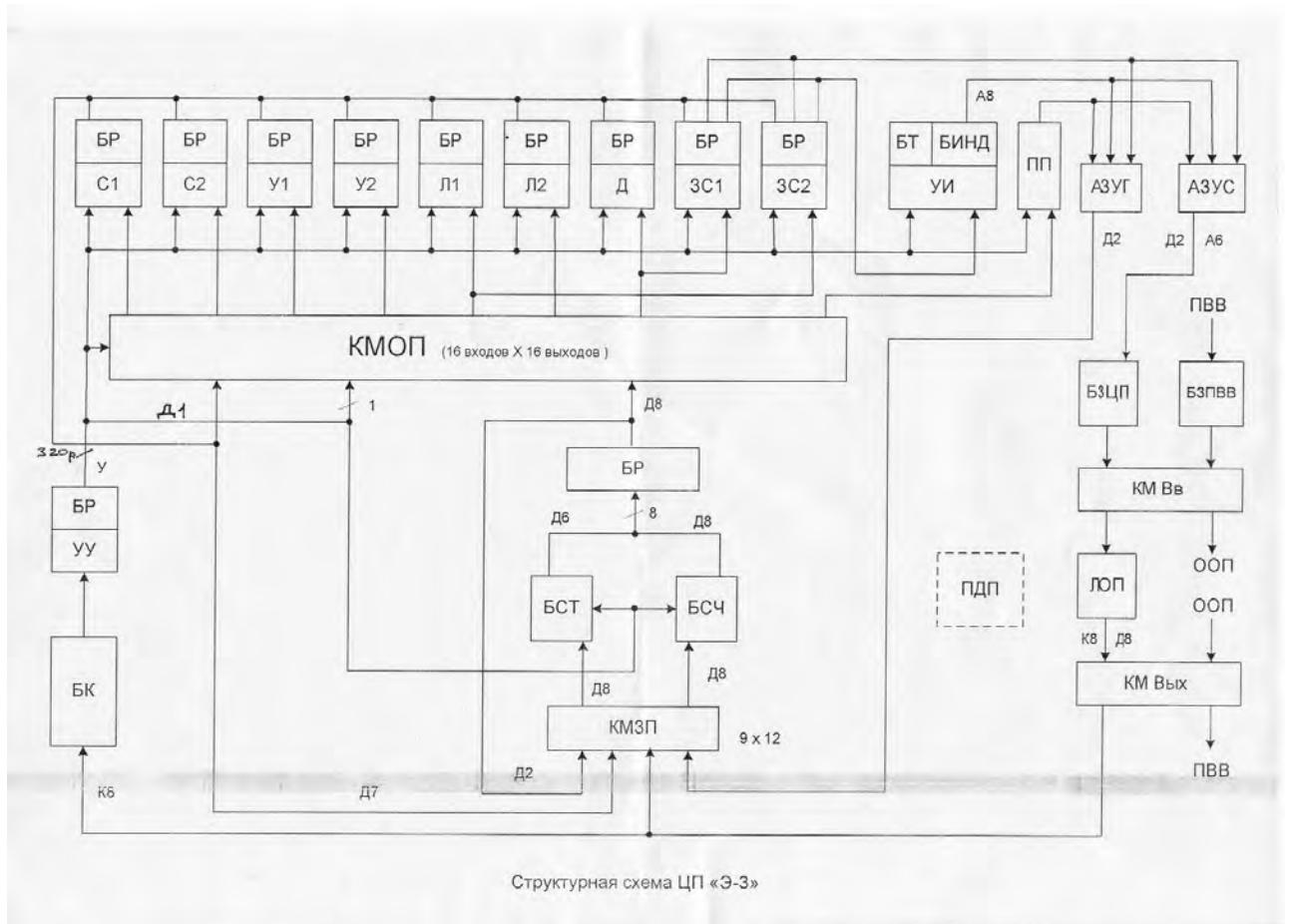

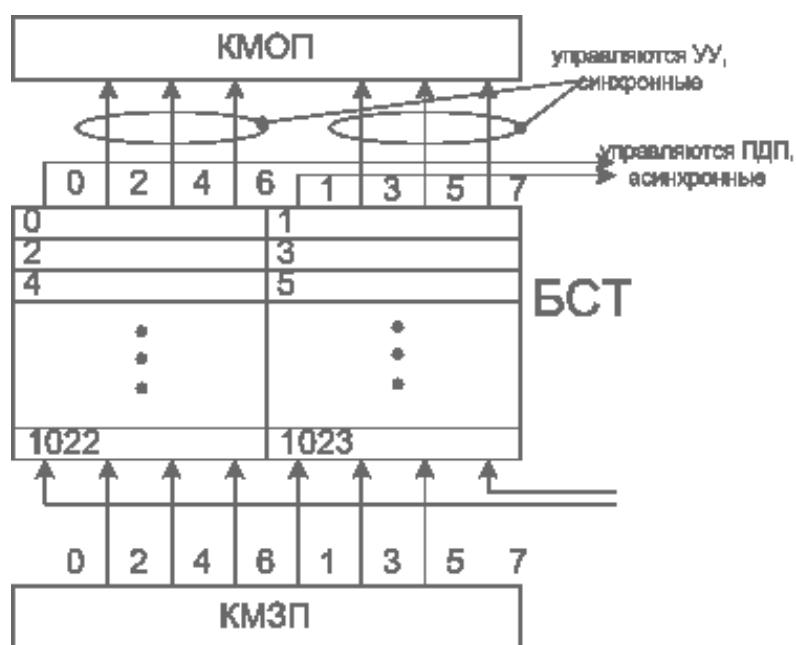

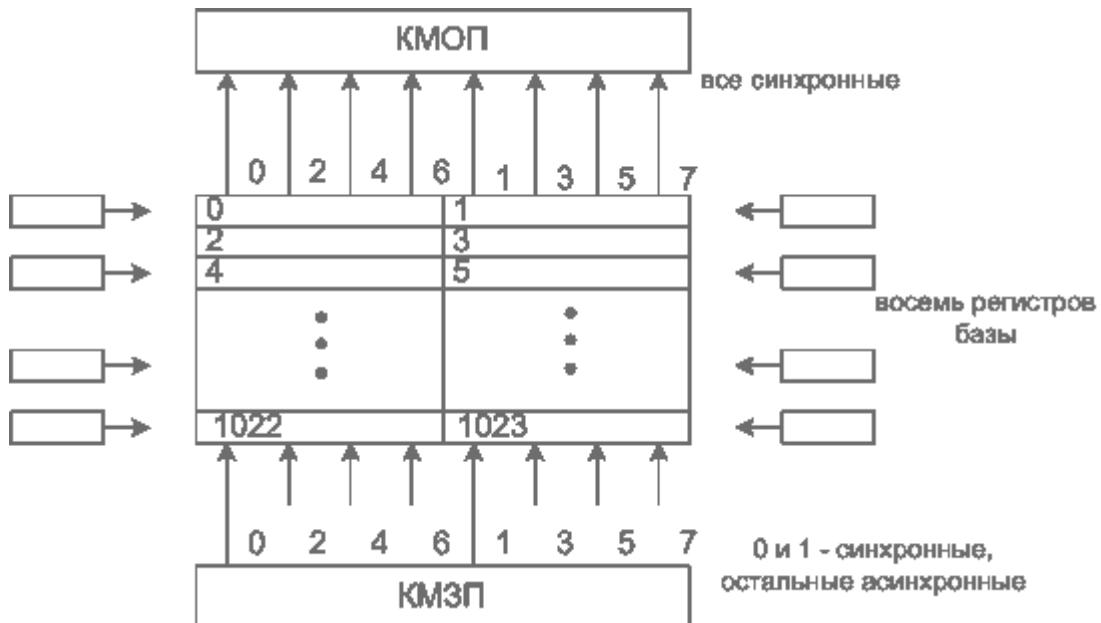

| 24.2.2         | Структурная схема ЦП «Эльбрус-3» .....                                   | 194 |

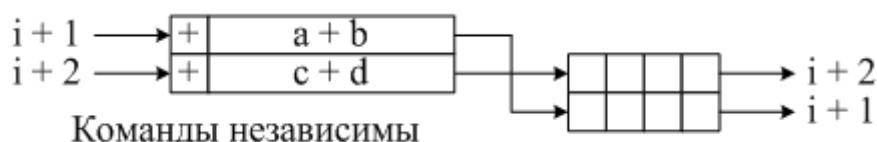

| 24.2.3         | Структура распакованной команды «Эльбрус-3».....                         | 198 |

# Лекция 1

## 1. Основные понятия в области вычислительных систем

### 1.1 Введение. Основные определения

Термин «Вычислительная система» (ВС) появился в 60-е годы, когда понятие «Электронная вычислительная машина» (ЭВМ) уже не отражало с одной стороны всего многообразия средств вычислительной техники, а с другой стороны не различало их по степени сложности. Поэтому интуитивно можно считать, что *вычислительная система* - это объект, относящийся к средствам вычислительной техники (СВТ) и имеющий более сложную организацию, чем ЭВМ. К сожалению, до настоящего времени сколько-нибудь удовлетворяющего всех разработчиков СВТ определения ВС не установлено. Однако существует необходимость хотя бы с методической точки зрения различать объекты, относящиеся к понятию ЭВМ и к понятию ВС, при этом понимая, что чёткой грани, разделяющей эти объекты провести невозможно.

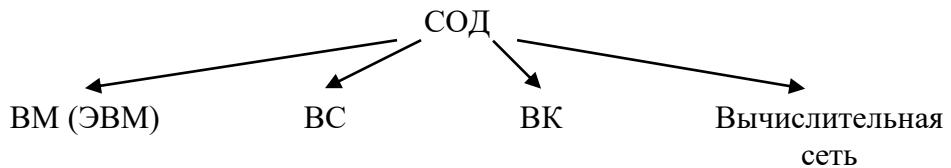

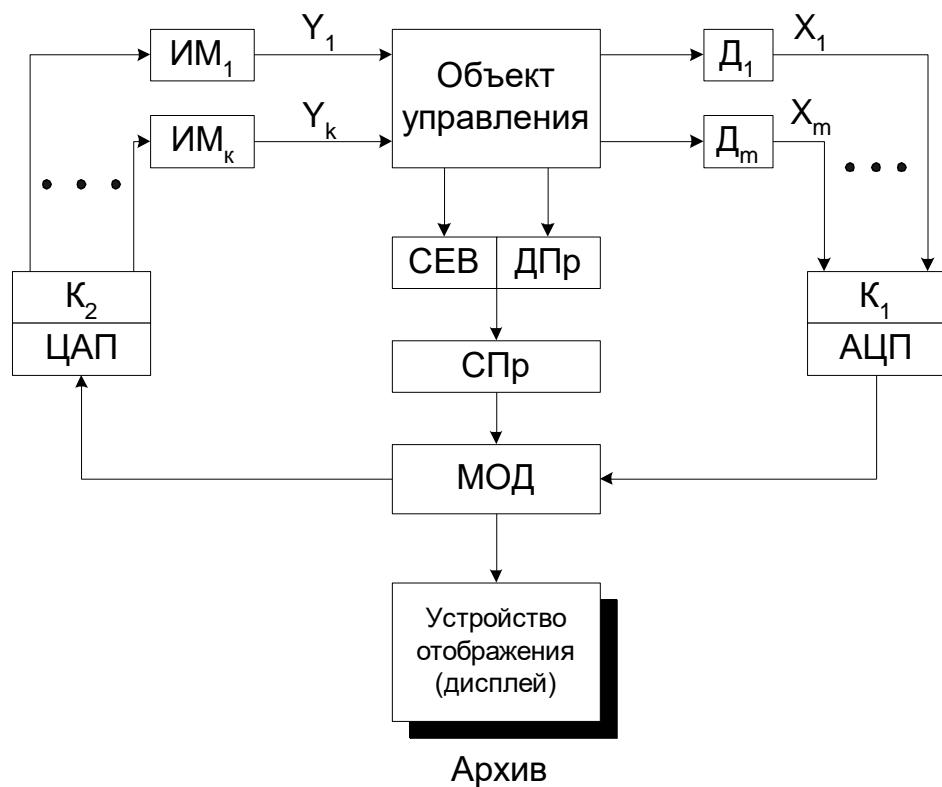

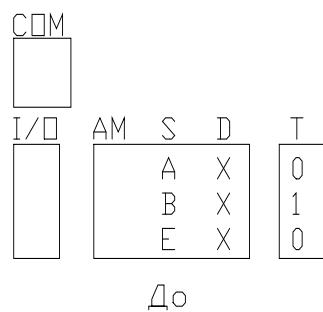

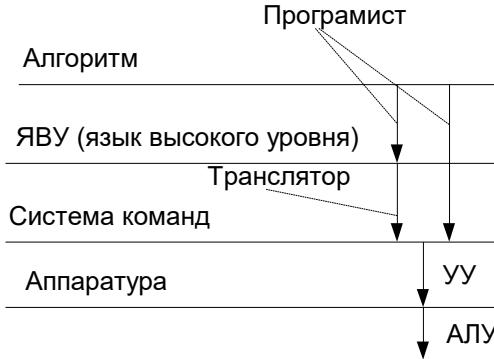

Попытаемся внести смысловой оттенок в определение ВС через разъяснение нашего понимания таких терминов, как «система», «структура», «архитектура», толкование которых само по себе вызывает много споров у специалистов по вычислительной технике. В данной области техники термин «система» используется чрезвычайно широко и имеет множество смысловых оттенков. Мы будем понимать под системой объект, представляющий собой единое целое, предназначенный для выполнения определенных функций и состоящий из множества связанных между собой элементов. Под элементами могут пониматься как аппаратные, так и программные средства. Следовательно, такие объекты, как ЭВМ и ВС, являются системами, предназначенными для автоматизированной обработки данных и представляющие собой совокупность программных и аппаратных средств. Для их обозначения используется понятие «система обработки данных» (СОД). На рис. 1.1 представлены виды систем обработки данных, в том числе ВМ (синоним ЭВМ) – вычислительная машина, ВК – вычислительный комплекс.

Рис. 1.1 Виды систем обработки данных

*Структура СОД* обычно определяется в виде совокупности трёх категорий: *множество аппаратных элементов*, входящих в состав системы, *множество связей*, объединяющих эти элементы, и *алгоритм функционирования системы*. В контексте проектирования аппаратных

средств вычислительной системы термин «структура» используется для описания принципа действия, конфигурации и взаимного соединения устройств системы.

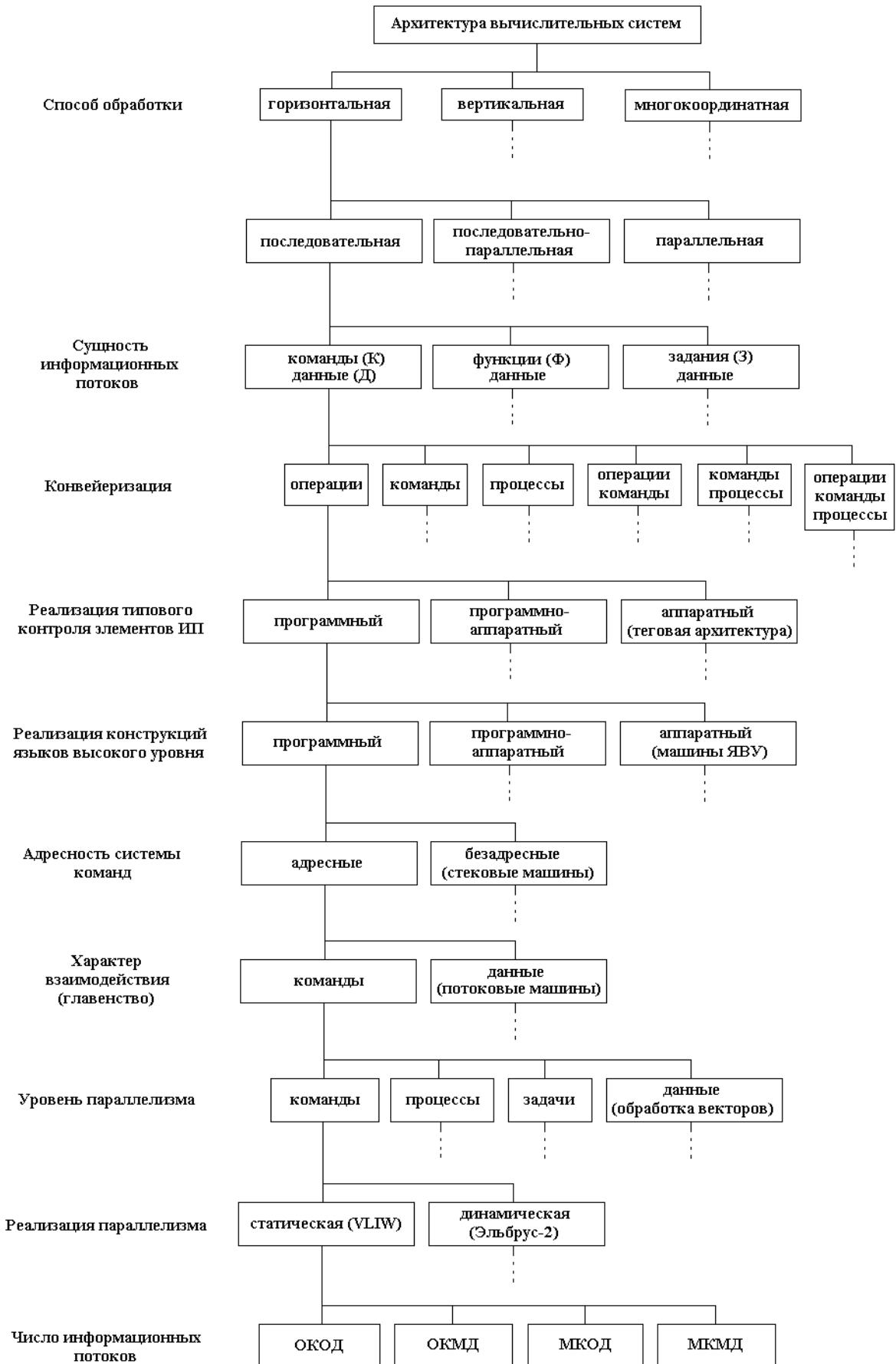

*Архитектура СОД* может быть определена как совокупность тоже трёх категорий: *сущность информационных потоков*, например, существование двух потоков – команд и данных, *характер взаимодействия информационных потоков*, например, жесткая последовательность команд управляет обработкой данных, *способ обработки данных*, например, последовательный или параллельный. Следовательно, понятие архитектуры отображает обобщенное определение системы с точки зрения существующих в ней информационных потоков и способа их обработки.

Общность архитектуры разных ЭВМ и ВС обеспечивает их совместимость с точки зрения пользователя. Реализация конкретной архитектуры ЭВМ и ВС может быть различной: использование разных по физической природе элементов, применение оригинальных решений при разработке устройств системы, её структуры, что приводит, например, к различию систем по стоимости, производительности, но не меняет принципы обработки данных. В настоящее время можно выделить три вида понятий, связанных с термином «архитектура»: фоннеймановская архитектура, усовершенствованная фоннеймановская архитектура, нетрадиционная архитектура.

Первый вид определяет класс объектов с архитектурой, которая основана на использовании двух информационных потоков - команд и данных, с чисто последовательным характером обработки данных под управлением заранее составленной последовательности команд (программы). Понятие «усовершенствованная фоннеймановская архитектура» связано с реализацией различных методов распараллеливания потока обработки данных с целью увеличения производительности системы, но не нарушая принципа программного управления. В этом случае можно говорить о том, что этот вид архитектуры отличается от первого только увеличением числа потоков команд и данных в любых сочетаниях. Естественно, в зависимости от числа потоков команд и данных, примененного метода распараллеливания и характера управления множествами потоков «усовершенствование» архитектуры может идти различными путями, приводя к появлению новых типов архитектур в рамках данного вида.

Понятие «нетрадиционная архитектура» связано, в частности, с так называемыми потоковыми машинами, которые отличаются новым принципом управления вычислительным процессом и разделяются на два типа архитектур: управляемые потоком данных (нет счетчика команд; устройство управления сложное, обычно выполненное на АЗУ; программы нет как таковой) и управляемые запросами. При этом, по аналогии с фоннеймановской архитектурой, организация вычислений может быть «последовательной» (здесь этот термин используется только с точки зрения аналогии, так как по своей сути потоковые машины строятся с

использованием всех видов параллелизма, поэтому последовательные потоковые машины можно рассматривать как вырожденный случай) и параллельной.

Таким образом, определяя понятие «вычислительная система» с точки зрения архитектуры, можно сделать вывод о том, что этот класс СОД должен обладать либо усовершенствованной фоннеймановской архитектурой, либо нетрадиционной с параллельной организацией вычислений. При этом ЭВМ обладают либо фоннеймановской архитектурой, либо нетрадиционной с последовательной организацией вычислительного процесса.

Для того, чтобы дать более точное определение ЭВМ и ВС, необходимо определить их место среди таких объектов СОД, как ВК и вычислительная сеть. Для этого дадим следующие определения, введённые профессором кафедры ВМСиС Дерюгиным А.А [1] при участии автора.

1. *Процессор, центральный процессор, центральное процессорное устройство* (обозначение на схемах Р, СР, CPU) – основная часть ЭВМ, предназначенная для обработки данных и управления этой обработкой в соответствии с последовательностью команд программы. Такой процессор по умолчанию является скалярным. В состав процессора входят:

а) арифметико-логическое устройство (ALU), состоящее из одного или нескольких блоков обработки числовых данных с фиксированной и плавающей запятой, блока логических операций, сдвига данных и др.;

б) устройства управления (CU – control unit), содержащее счетчик команд (IP – instruction pointer), регистр команд (инструкций, RGI), часто буфер команд, блок преобразования кода операций в коды микроопераций, т.е. в последовательности управляющих сигналов, соответствующих микрооперациям, как для управления работой процессора, так и для управления другими устройствами ЭВМ;

в) блок регистров, включая адресуемые регистры общего назначения (регистровую память RGM), регистры управления, в том числе регистр флагов (признаков) и др., а также неадресуемые регистры (дескрипторы и др.);

г) интерфейсный блок (IU), предназначенный для реализации связей процессора с другими устройствами ЭВМ. В состав этого блока входит, в частности, узел управления памятью (менеджер памяти), предназначенный для формирования из кода адреса операнда, указанного в команде, физического адреса ячейки памяти, в которой хранится требуемый операнд.

## Виды процессоров

- 1.1. Суперскалярный процессор (SSP) – процессор, допускающий параллельное (одновременное) выполнение нескольких команд программы. Такой процессор может содержать несколько конвейеров обработки данных.

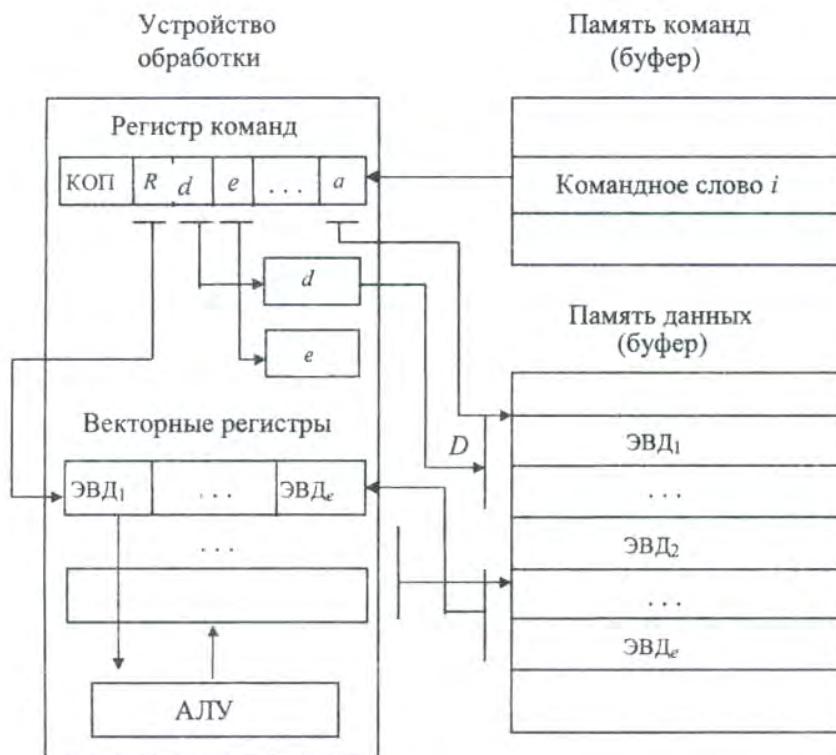

- 1.2. Векторный процессор (VP) – процессор, содержащий специальные блоки обработки данных, предназначенные для выполнения, как

скалярных операций, так и операций над векторами в соответствии с векторными командами, входящими в состав системы команд процессора, а также блок векторных регистров (VRG).

- 1.3. Матричный процессор (MP) – многопроцессорное устройство, предназначенное для выполнения операций над векторами и матрицами.

- 1.4. Ассоциативный процессор (AP) – специализированный процессор, реализованный на базе ассоциативного запоминающего устройства и предназначенный для одновременного выполнения операций над массивами данных последовательно по разрядам этих данных.

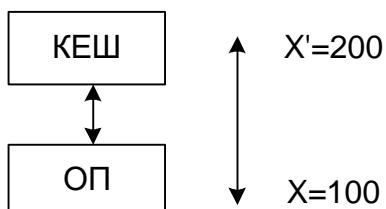

2. Кэш-память (CM) – быстродействующая буферная память небольшой ёмкости, в которой хранятся команды и данные, необходимые для использования в течение текущего интервала времени. Содержимое CM дублирует содержимое основной (большой) памяти (BM – base memory) и меняется в процессе работы ЭВМ автоматически аппаратным способом. Обмен данными между CM и BM производится строками (блоками). Обычно это 16...64 байта. В состав CM входят: собственно кэш-память и местное устройство управления, включая таблицу, в которой хранятся адреса тех блоков, которые находятся в кэш-памяти в данный момент. В зависимости от «удаления» от процессора различают CM первого и второго уровней (L1 и L2, L – level). Кэш-память первого уровня может быть общей для команд и данных или раздельной для команд и данных. Кэш-память второго уровня, как правило, общая для команд и данных.

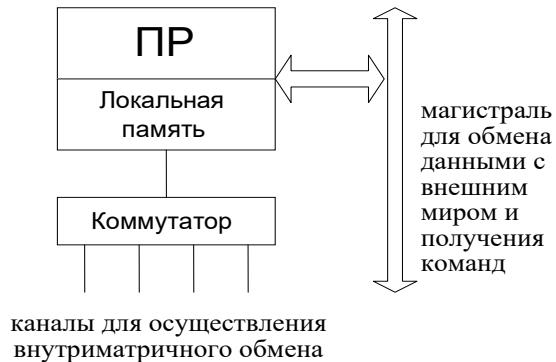

3. Процессорный модуль (PM), вычислительный модуль – устройство, содержащее процессор, кэш-память или, например, локальную память (LM).

4. Внутренняя память (IM – internal memory) – память, предназначенная для приёма, хранения и выдачи информации, непосредственно используемой (адресуемой) процессором. IM – это RGM+CM+BM.

5. Внешняя память (EM – external memory) – память, предназначенная для длительного хранения больших объёмов информации. Для использования этой информации её необходимо переместить во внутреннюю память средствами операционной системы. Внутренняя память является буферной памятью по отношению к внешней памяти.

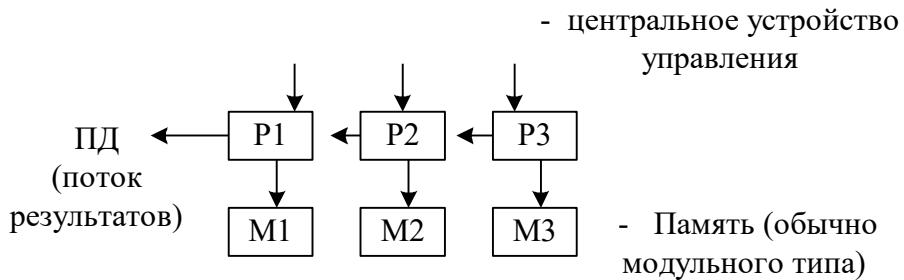

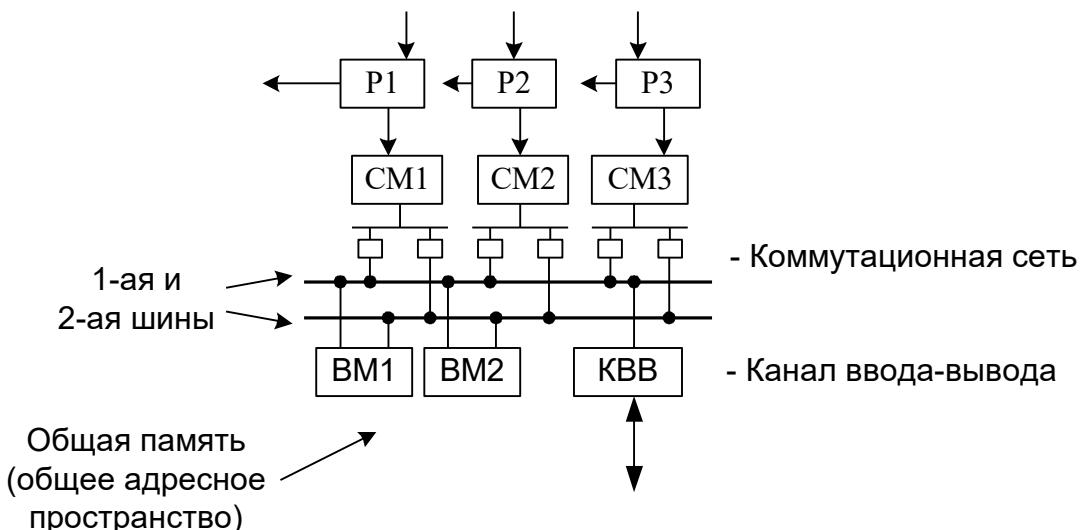

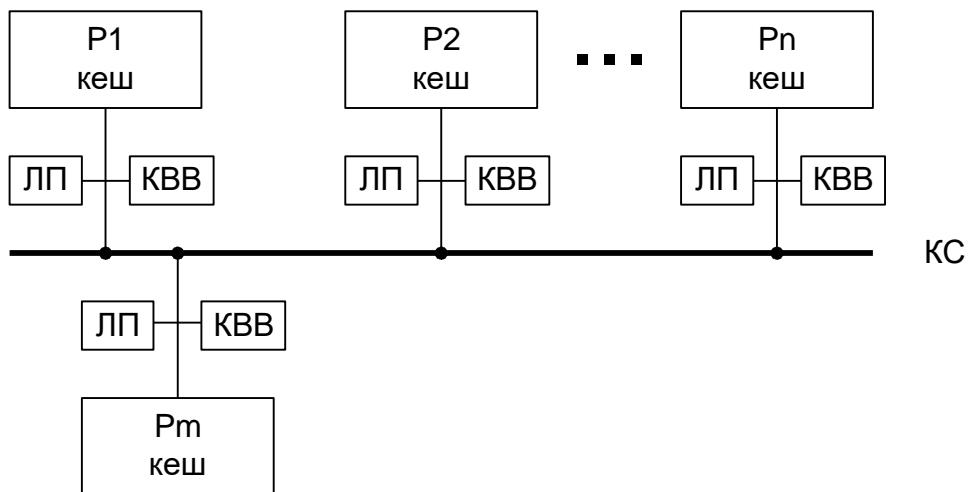

6. Многопроцессорный модуль (MPM) – функциональное устройство, содержащее вычислительные модули, соединённые с кэш-памятью второго уровня. Из PM и MPM могут быть построены многопроцессорные вычислительные системы (МВС) с двухуровневой или трёхуровневой общей внутренней разделяемой памятью.

7. Общая или разделяемая память МВС – это внутренняя память, к ячейкам которой может обращаться любой процессор, входящий в состав МВС.

8. Локальная память (LM) процессора, входящего в состав МВС, - это внутренняя память, к ячейкам которой может обращаться только данный процессор. Адресные пространства для общей и локальной памяти не пересекаются.

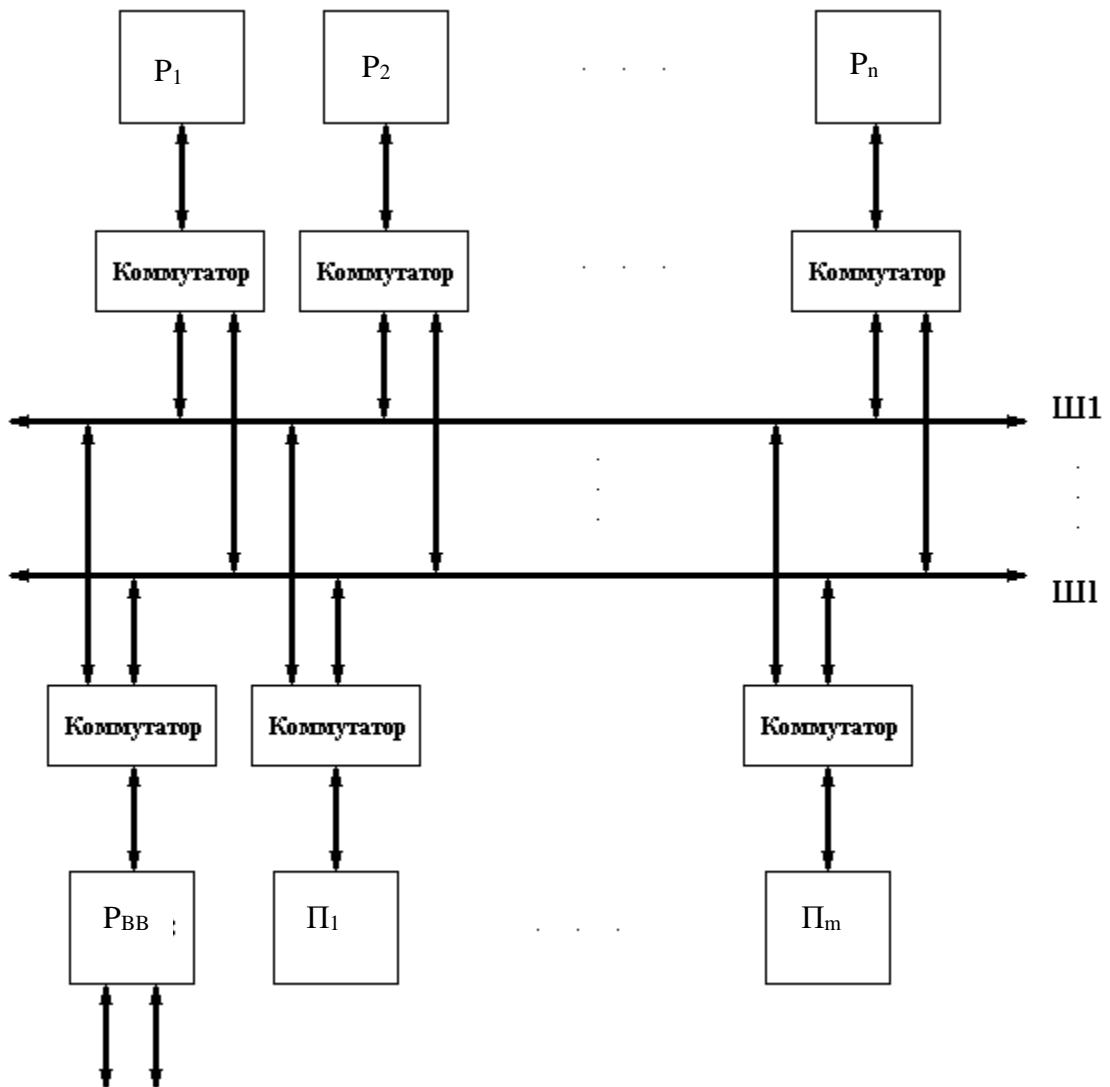

9. Коммутатор (SW) МВС – аппаратные средства, обеспечивающие взаимодействие между компонентами МВС. В состав коммутатора в явном или неявном виде входит арбитр.

В состав СОД могут входить так называемые *вспомогательные процессоры*. К ним относятся управляющие процессоры, обеспечивающие реализацию функций, служебных по отношению к самой СОД, сервисные процессоры для выполнения функций контроля и диагностики СОД, процессоры ввода-вывода, процессоры телеобработки данных и т.д.

Совокупность любых процессоров любого количества, оперативной памяти и каналов ввода-вывода назовём *центральной частью (ЦЧ)* СОД.

СОД, включающую в себя одну центральную часть, в состав которой входит один процессор обработки данных любого вида и возможно один или несколько вспомогательных процессоров р, обеспечивающих максимально эффективную работу первого, а также периферийные устройства, назовём *электронной вычислительной машиной (ЭВМ)*.

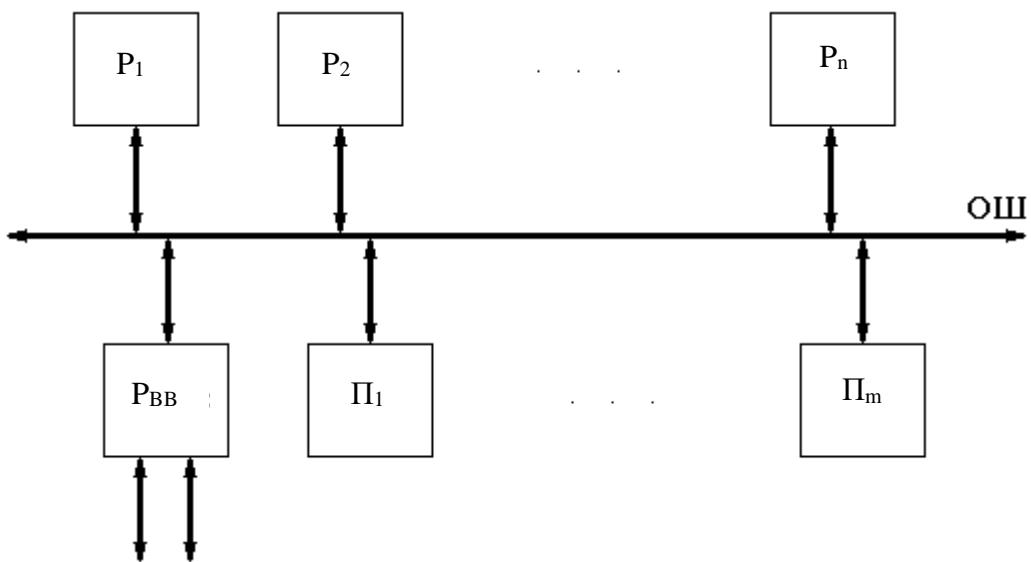

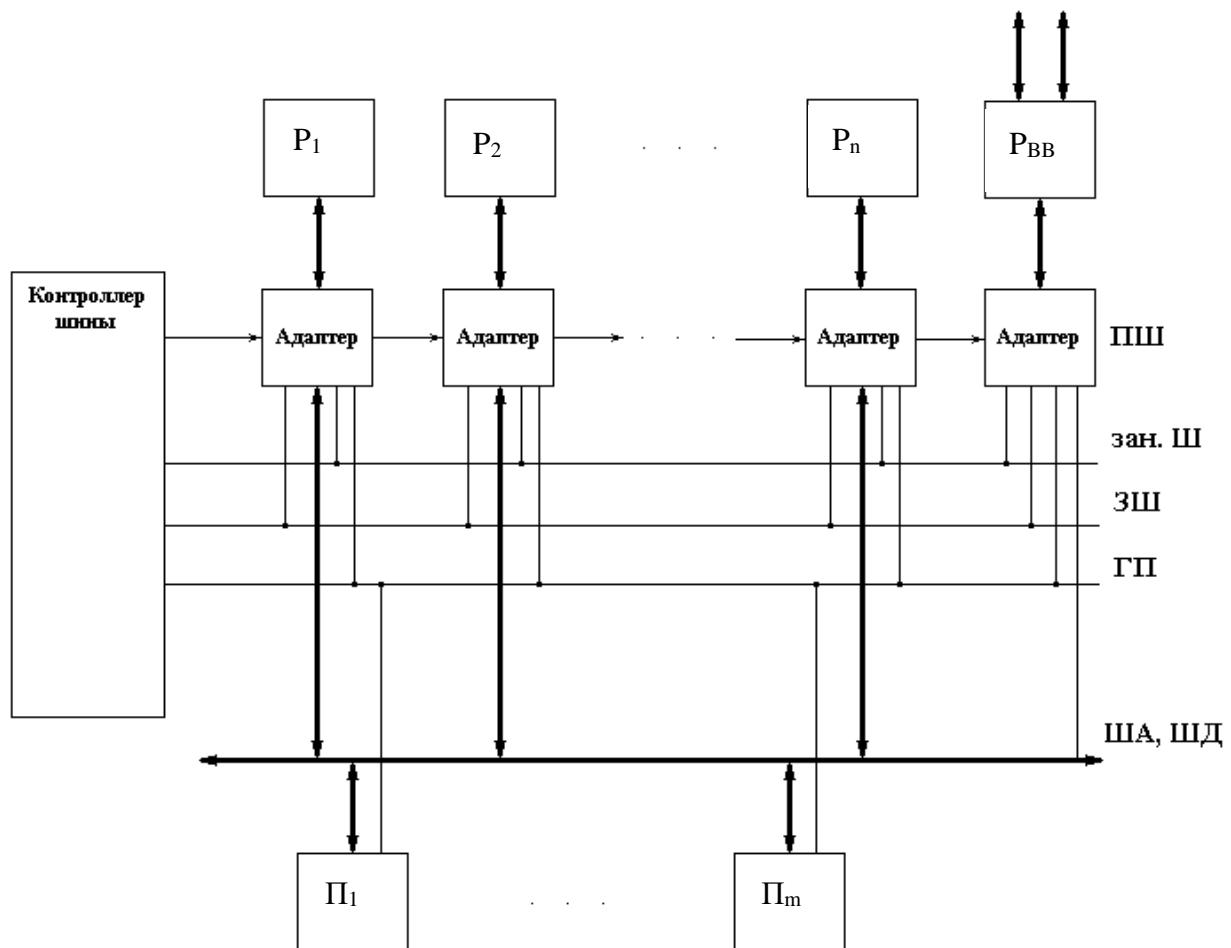

СОД, включающую в себя одну ЦЧ, но имеющую более одного процессора обработки данных любого вида, периферийные устройства, назовём *вычислительной системой (ВС)*.

СОД, включающую в себя несколько ЦЧ, объединенных по каналам ввода-вывода, и общие для них периферийные устройства, назовём *вычислительным комплексом (ВК)*.

Множество ЭВМ, ВС и ВК объединённых линиями связи, назовём *вычислительной сетью*.

Настоящее учебное пособие посвящено, в основном, отдельным вопросам, связанным с вычислительными системами с усовершенствованной фоннеймановской архитектурой. При анализе таких систем для количественной оценки их эффективности обычно используется такой показатель, как *производительность*. Приведем наше толкование данного показателя. При этом будем различать два взаимосвязанных вопроса: какое качество системы отображает это понятие и в чём можно измерить это качество. Отвечая на эти вопросы, можно определить производительность как характеристику вычислительной мощности системы, определяющую количество выполненной работы за единицу времени. Таким образом, если имеем в виду вычислительную систему, то под работой можно понимать решение задач. В этом случае производительность есть число задач, выполненных системой в единицу времени. Следовательно,

производительность системы будет различной для задач различных классов. Существует большое число методов оценки производительности ВС, связанных с тем или иным классом задач, однако главные из них основаны на использовании специально созданных тестов. Для того, чтобы оценить производительность системы, не привязываясь к классу задач, иногда используют такой показатель, как *быстродействие*. Хотя этот показатель отражает только техническую сторону вычислительной системы, а иногда характеристику только основного элемента системы - процессора, он достаточно широко распространен. Если в первых ЭВМ быстродействие измерялось в количестве коротких операций в секунду, например, типа «регистр-регистр» или «сложение с фиксированной точкой», то современные ЭВМ и ВС характеризуются числом выполняемых операций с плавающей точкой в секунду, которые получили название флопов (FLOPS). Для специализированных ВС используются другие единицы измерения, например характерные для них операции, транзакции и т.д.

Данный курс лекций поможет студентам ответить на такие вопросы как: зачем нужны ВС всё большей и большей производительности, как видоизменяются структура и архитектура процессора и самой ВС с целью повышения эффективности использования их аппаратных средств, какими свойствами должно обладать их программное обеспечение, какие новые идеи существуют в области разработки высокопроизводительных вычислительных систем. И как показывает опыт развития средств вычислительной техники, вопросов, на которые пока нет ответов, появляется всё больше и больше.

## Лекция 2

### 1.2 Понятие Фон-неймановской архитектуры

Джон фон Нейман (Янош 1903-1957) родился в Будапеште, а с 1930 г. жил и работал в США. По профессии математик и физик. Предложил принцип обработки данных и архитектуру программного автомата, который получил название неймановской машины. Построение ЭВМ, основанной на этом принципе, базируется на идее автоматизации вычислений под управлением программы (последовательность инструкций) и использует две фундаментальные мысли.

Первая из них состоит в том, что программа вводится через те же внешние устройства и хранится в той же памяти, что и исходные данные. Это обеспечивает оперативную перестройку машины с одной задачи на другую без внесения каких-либо изменений в схему машины и её коммутацию, делая машину универсальным вычислительным инструментом. Термин универсальная ЭВМ широко использовался в последующие годы.

Вторая состоит в том, что инструкции, составляющие программу вычислений, закодированы в виде чисел и по форме ничем не отличаются от тех чисел, с которыми оперирует машина. Это дает возможность при выполнении некоторой инструкции прочесть другую или, в частном случае, ту же инструкцию как число, переслать её в арифметическое устройство, произвести там с ней некоторые операции и вернуть на своё место в запоминающем устройстве (памяти) в преобразованном виде. Когда в следующий раз устройство управления обратится к данной ячейке памяти за инструкцией, а не за операндом, то исполняться будет уже не исходная, а преобразованная инструкция. Таким образом, при исполнении некоторой программы может одновременно происходить её преобразование, либо формирование новой программы. Следовательно, можно сказать, что неймановская машина по своей сути обладает элементами интеллектуальной системы.

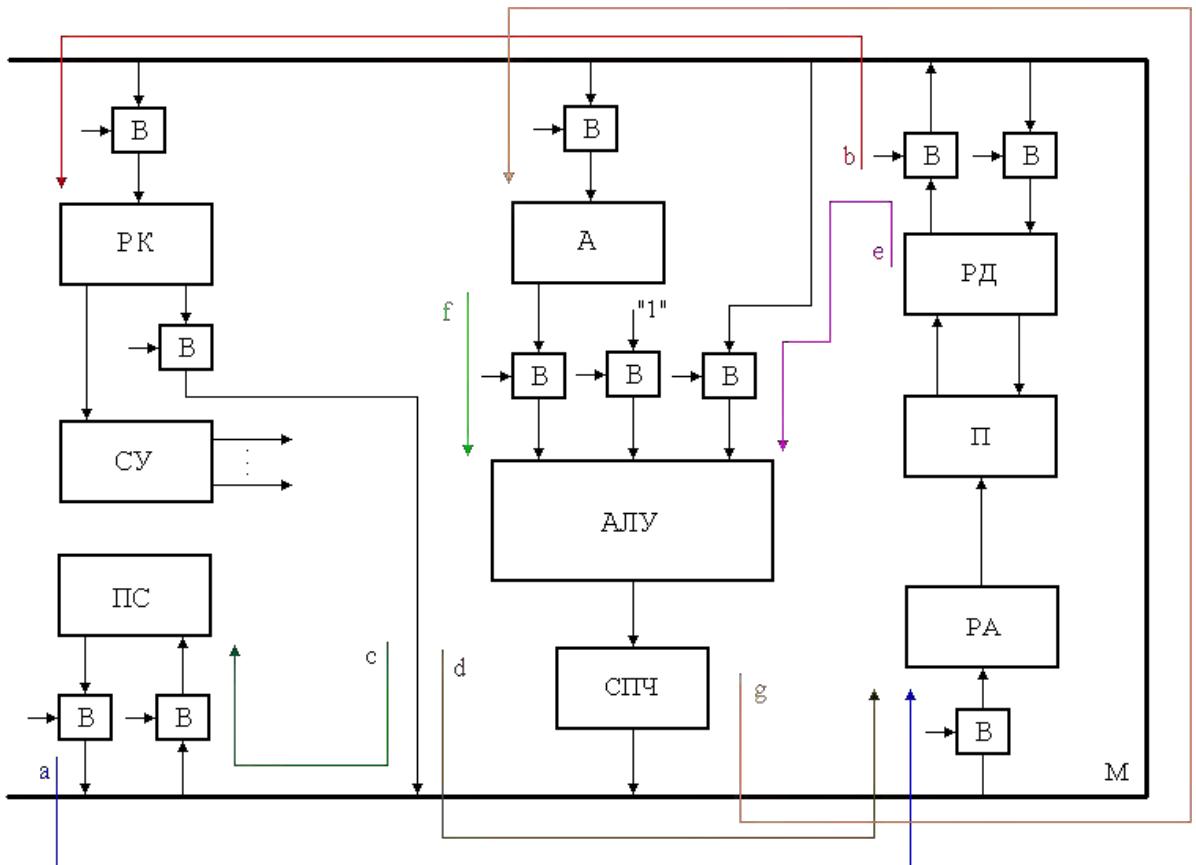

Прежде чем рассматривать последующие усовершенствования неймановской машины, напомним принципы её действия. Основными элементами базового варианта неймановской машины, представленного на рис. 1.2, являются:

- программный счётчик (ПС);

- регистр команд (РК);

- схема управления (СУ);

- арифметико-логическое устройство (АЛУ);

- аккумулятор (А);

- схемы представления чисел в дополнительном коде с регистром сдвига (СПЧ);

- память инструкций (команд) и данных (П);

- регистр адреса (РА);

- регистр данных (РД);

Рис. 1.2 Базовый вариант неймановской машины

- совокупность вентильных групп (В), на которые поступают управляющие сигналы из СУ;

- внутренняя машинная магистраль (М).

Процесс обработки данных в такой машине чисто последовательный и выполнение каждой команды разбивается на строго определенный ряд следующих друг за другом действий. Если за точку отсчета принять такое состояние машины, при котором в ПС установлен адрес следующей команды, то эти действия (шаги) следующие:

- по адресу команды, находящемуся в ПС, происходит обращение к П с использованием РА, после чего сама команда оказывается в РД;

- код команды заносится из РД в РК;

- в случае команды условного (безусловного) перехода, формирование номера следующей команды и занесение его в ПС;

- в случае исполнительной команды, обращение в память за операндом по адресу, расположенному в коде команды или по адресу, вычисленному специальной схемой;

- занесение операнда из РД в АЛУ;

- занесение операнда из А в АЛУ;

- занесение результата операции из СПЧ в А.

### **1.3 Парадигмы Фон-неймановской архитектуры.**

Существуют две парадигмы, на которых базируется так называемая неймановская архитектура.

1) Входные данные и инструкции поступают по одному и тому же каналу и хранятся в одной и той же памяти.

2) Управление выполнением последовательности команд осуществляется программным счётчиком (ПС).

Сама команда, как это было отмечено выше, выполняется то же в виде последовательности шагов, число которых в современных ЭВМ может отличаться от приведённого примера, но суть их последовательности при выполнении одной команды остаётся неизменной.

Следовательно, главное определение неймановской машины – это последовательная машина.

### **1.4 Особенности Фон-неймановской архитектуры**

Анализ особенностей функционирования неймановской архитектуры показывает, что чисто последовательный характер обработки данных приводит к тому, что в каждый момент времени (применительно к процессору момент времени должен рассматриваться как машинный такт) функционирует только определённая часть аппаратуры, выполняющая соответствующие действия в рамках одного из шагов выполнения команды. Остальная часть аппаратуры простаивает. Именно этот вывод и до сих пор служит для широкого поля деятельности в совершенствовании технических характеристик систем обработки данных. С другой стороны, анализируя прикладные программы, созданные для реализации на ЭВМ, можно согласиться с выводами ученых, например, Прангишвилли И. В., которые утверждают, что любая программа содержит такую часть, которую можно распараллелить. Именно в этом состоит основное зерно, лежащее в основе усовершенствования неймановской архитектуры.

Рассматривая в целом такую СОД как ЭВМ с неймановской архитектурой, можно привести такие основные её проблемы. Здесь под проблемами понимаются её узкие места, не позволяющие эффективно использовать аппаратно-программные средства ЭВМ.

1. Программные коды (команды) вместе с данными хранятся в одной и той же памяти.

Это приводит к тому, что в процессе выполнения одной команды необходимо несколько раз обратится последовательно к одной памяти, что значительно замедляет процесс обработки данных.

2. Линейное пространство адресов, которым присваиваются порядковые номера 0, 1, 2, 3... .

Это свойство ограничивает эффективность применения памяти с модульной организацией.

3. Каждая программа выполняется последовательно, начиная с самой первой команды, если нет специального указания (команды перехода). Это свойство ограничивает возможности использования характера параллельности выполняемых программ.

4. Последовательное выполнение обработки в неймановской архитектуре приводит к последовательному изменению состояния машины путём изменения содержимого памяти. Это явление носит название *побочного эффекта*. Поскольку вычисления выполняются с побочным эффектом, то результат операции нужно каждый раз записывать в память.

5. Отсутствие различий в машинном представлении данных и команд. В этом случае, в частности, возникают проблемы, усложняющие разработку программного обеспечения. Наличие разрыва между понятиями операций и их объектов на языке программирования высокого уровня и понятиями операций и их объектов, определяемыми архитектурой компьютера, называется *семантическим разрывом*.

6. Отсутствие различий в семантике данных. Иначе говоря, если на языке высокого уровня можно описать различные типы данных, то в неймановской архитектуре разницы в представлении типов данных нет. Поэтому каждый раз, когда необходимо выполнить те или иные операции над данными нужно либо программно, либо аппаратно проконтролировать их тип.

Какие существуют способы для "смягчения" влияния узких мест рассматриваемой архитектуры на её производительность?

Наиболее эффективный способ - это увеличение пропускной способности тракта между процессором и памятью. Сюда входит введение многоуровневой памяти, в том числе КЭШ памяти и разделение её на КЭШ-команд и КЭШ-данных, применение многопортовой памяти, использование принципа расслоения при модульной организации памяти, применение механизмов реализации виртуальной памяти.

Что касается линейного адресного пространства, то его преобразование в структурированное пространство памяти было предложено г. Илиффом в 1972 г. Его идея состоит в том, чтобы с помощью некоторого алгоритма добавлять ко всем элементам памяти информацию, показывающую атрибут этого элемента. Эта дополнительная информация получила название *tag* (тег-признак). Машины, основанные на использовании этого признака, называются *теговыми машинами*. В таких машинах различие типов данных поддерживается аппаратно, так как каждый тип данных характеризуется своим тегом. Это в свою очередь приводит к тому, что однотипные команды, отличающиеся только типом операндов, никак не

различаются. Следовательно, число команд в системе команд таких машин сокращается.

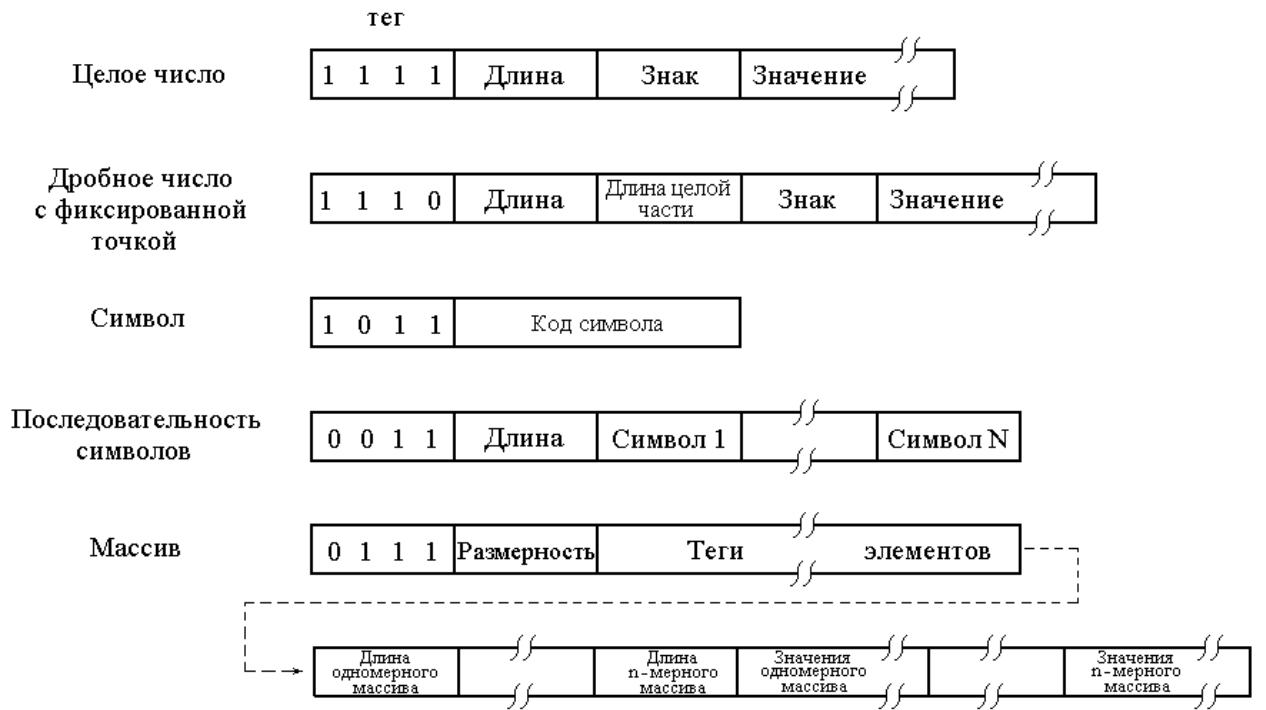

Примером машины со структурированной памятью является SWARD-машина, предложенная г. Майерсом. В SWARD-машине данные представлены структурными элементами, называемыми ячейками, которые состоят из поля тега и поля данных. Память разбита на 4-разрядные единицы. Ниже на рис. 1.3 приведены различные типы ячеек.

Рис.1.3 Типы ячеек SWARD-машины

Таким образом, применение тегов в том числе устраняет "отсутствие различий в семантике данных" на уровне их машинного представления.

Для улучшения производительности при использовании конвейера вводится блок предсказания ветвлений. Данный блок аппаратно подсчитывает число итераций для арифметических циклов и определяет момент следующего перехода. В случае перехода по признаку возможно лишь вероятностное предсказание. При этом собирается статистика предыдущих переходов.

Устранение побочного эффекта более сложная проблема, решение которой основано на создании архитектуры машины, реализующей так называемый функциональный язык (ФЯ). ФЯ предполагает отсутствие побочного эффекта (отсутствует оператор присваивания) и не влечёт за собой последовательное считывание и исполнение команды. Примерами ФЯ являются языки LISP и SALS. Программа состоит из множества равенств,

определяющих функции и описаний приложений этих функций при вводе данных. Например, в языке SALs функция fact, вычисляющая факториал, определяется следующим образом:

$$\begin{aligned} \text{fact } n \text{ where } \text{fact } 0 = 1 \\ \text{fact } n = n * \text{fact}(n-1) \end{aligned}$$

Следовательно, программа на ФЯ представляется некоторой функцией  $F$ , а выполнение программы определяется как результат действия этой функции (её оценка)  $F(x)$  по отношению к входу  $x$ .

## Лекция 3

### 2. Эволюция способов обработки данных

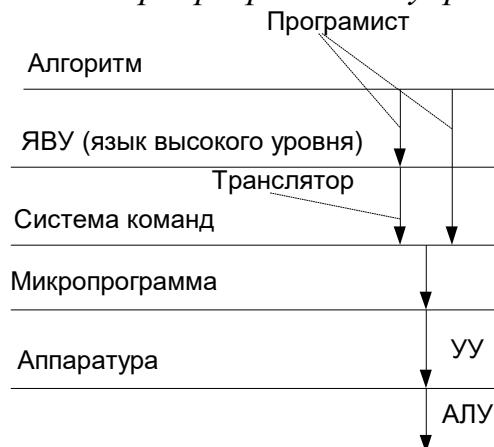

Обычно в учебной литературе, рассматривая эволюцию средств вычислительной техники, приводят критерии разбиения ЭВМ на поколения и их подробные характеристики. Поскольку данный курс лекций рассчитан на специалистов в области вычислительной техники, способных вести разработку аппаратных средств обработки данных, обратим более пристальное внимание на эволюцию способов обработки данных и механизмов их обеспечивающих.

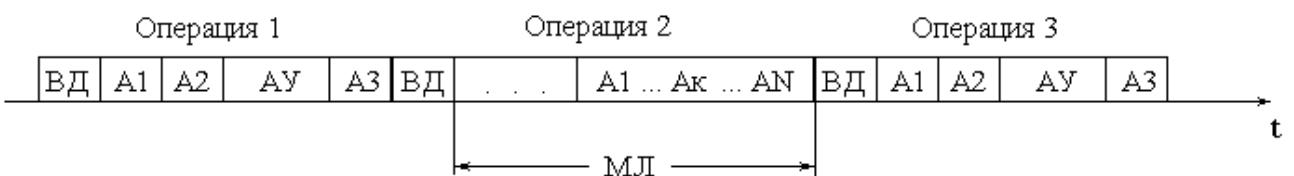

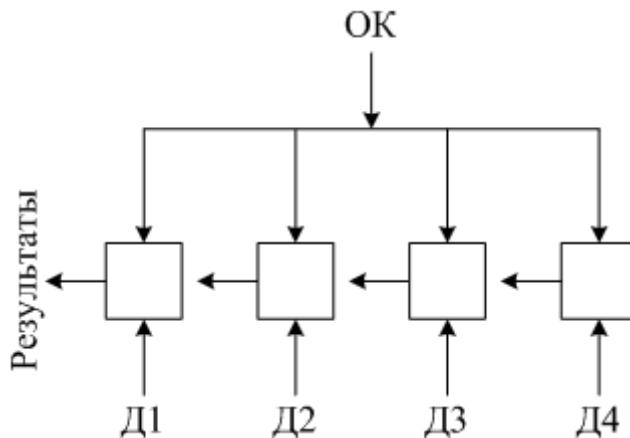

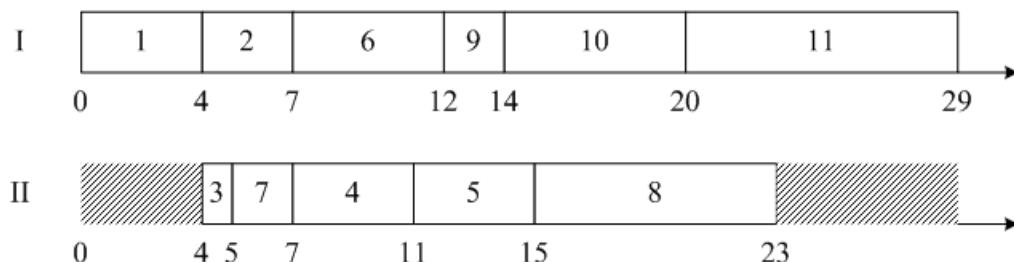

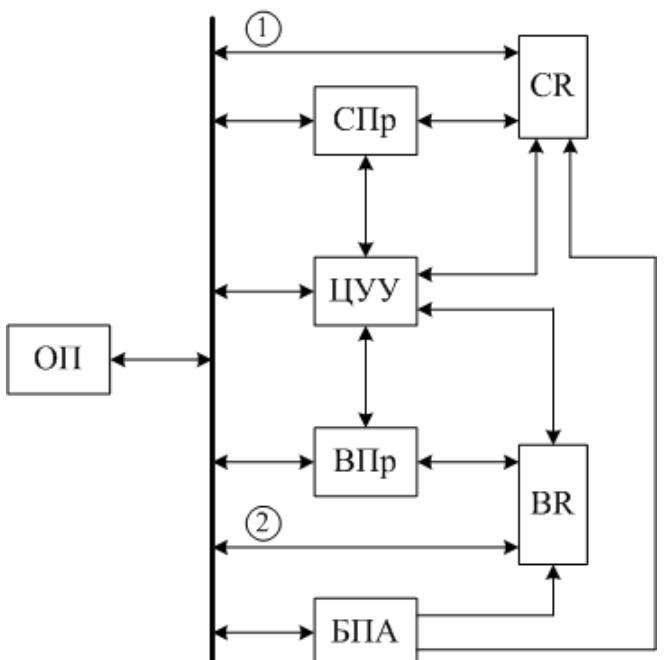

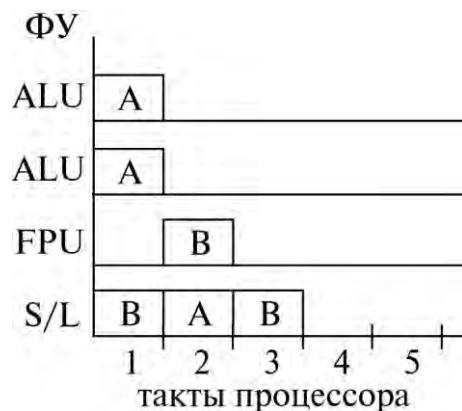

Разделим все способы обработки данных на два класса - *скалярная обработка* и *векторная обработка*. Исторически всё начиналось со скалярной обработки, которая реализовывалась с помощью базового варианта неймановской архитектуры. Причём первые ЭВМ имели в своём составе арифметическое устройство (АУ) последовательного действия. Например, Малая электронная счётная машина (МЭСМ), созданная под руководством академика С.А. Лебедева в 1950 г., имела производительность 50 оп/с, последовательное АУ с фиксированной запятой, всего 4 арифметические операции и одну управления при ёмкости оперативного запоминающего устройства (ОЗУ) в тридцать одно слово. В 1953 г. была создана Большая электронная счётная машина (БЭСМ), которая обладала производительностью 12000 оп/с, имела параллельное 39-разрядное АУ с плавающей запятой, ёмкость ОЗУ 1024 слова и выполняла 32 различные операции. БЭСМ имела достаточно развитую систему внешней памяти - барабан, ленту, устройства ввода/вывода на перфокартах и печатающее устройство. Согласно жёсткой последовательности работы устройств БЭСМ (см. рис. 2.1 ниже) сначала из ОЗУ считывался код команды, в соответствии с которой устройство управления организовывало необходимые обращения к ОЗУ за считыванием первого и второго операнда (скаляра), выдавало управляющие сигналы для выполнения операции на АУ, затем результат операции записывался в ОЗУ. Далее считывалась следующая команда. При обращении к ленте, барабану или внешним устройствам, устройство управления обеспечивало все операции поиска информации, её считывания и записи с применением АУ.

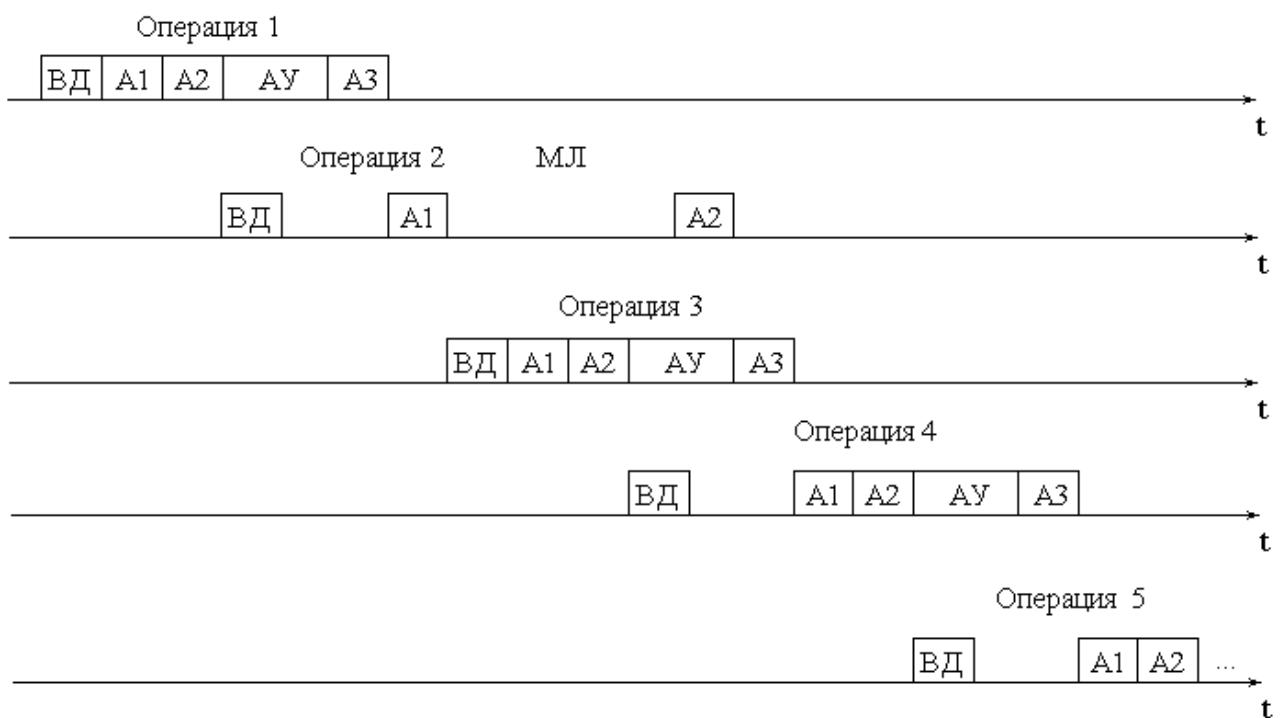

Рис 2.1 Временная диаграмма работы устройств БЭСМ

На приведённой временной диаграмме введены обозначения:

- ВД - выборка и дешифрация команды;

- А1 - выборка первого операнда;

- А2 - выборка второго операнда;

- АУ - выполнение соответствующей операции на АУ;

- АЗ - запись результата операции в ОЗУ;

- МЛ - операция записи и считывания с магнитной ленты.

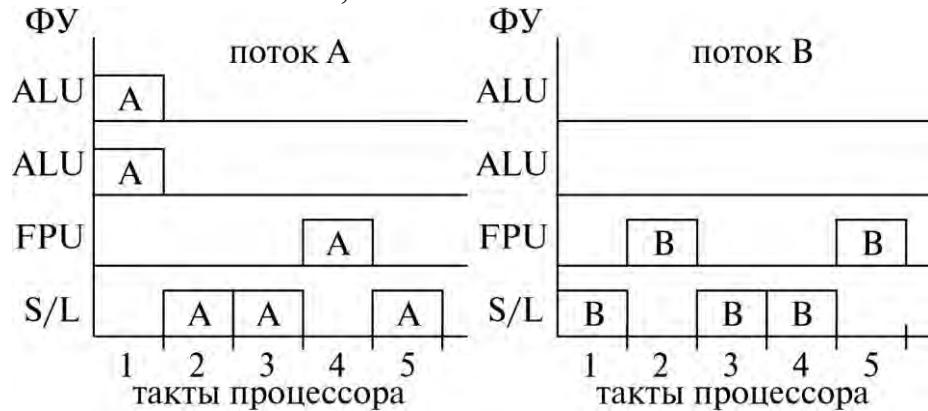

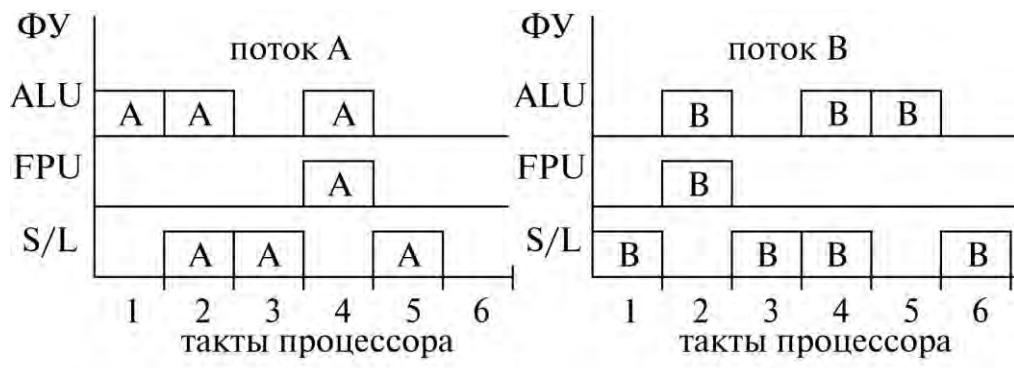

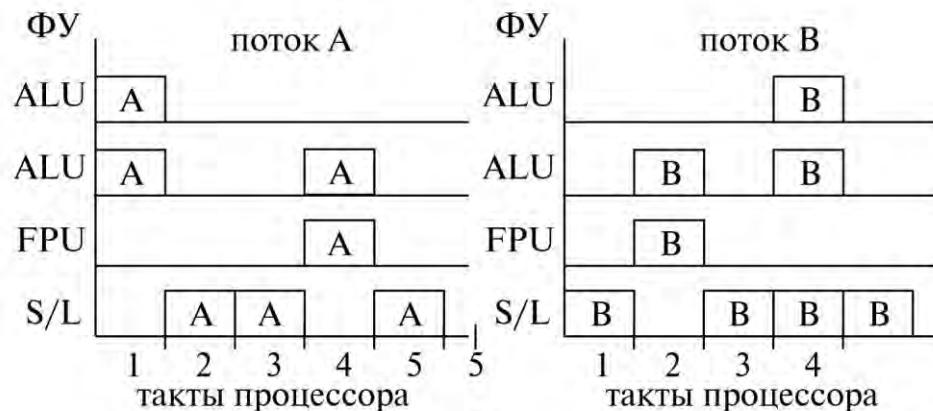

Следующим шагом в развитии скалярной обработки было введение механизма *предварительного просмотра команд*. Это позволило совместить такие этапы выполнения команды как её выборка и декодирование с исполнением предыдущей команды. Примерами машин с данным усовершенствованием служат ЭВМ М-40 и М-20, разработанные в Институте точной механики и вычислительной техники (ИТМ и ВТ) в 1953-58 годах. М-40 достигала производительности 40000 оп/с при ёмкости ОЗУ 4096 40-разрядных слов. Для достижения столь высокой производительности были существенно пересмотрены принципы организации системы управления ЭВМ. Каждое устройство машины получило своё автономное устройство управления, что позволило реализовать их параллельную работу. На рис. 2.2 ниже представлена временная диаграмма выполнения последовательности команд на ЭВМ М-40.

Рис. 2.2 Временная диаграмма выполнения последовательности команд на ЭВМ М-40

Как только была доказана высокая эффективность параллельной работы отдельных устройств ЭВМ, появилась идея введения множества автономных исполнительных функциональных блоков, каждый из которых предназначен для выполнения заданных операций. Таким образом, возник *функциональный параллелизм* на уровне операций. Примером ЭВМ, в которой применён так называемый параллельный процессор (многофункциональный процессорный модуль, содержащий несколько исполнительных функциональных блоков), может служить машина CDC-6600 (1964 г.). Она содержала 10 операционных исполнительных блоков - сумматор с плавающей точкой, умножитель с фиксированной точкой, сумматор с фиксированной точкой и др., которые параллельно выполняют соответствующие операции, совместно используя одни и те же регистры под управлением одного и того же устройства управления (УУ). УУ поддерживает в определенном состоянии операционные блоки (ОБ) и регистры, в процессе выполнения команд производит проверку занятости необходимых ОБ, управляет поступлением требуемых данных из других ОБ и памяти и передаёт управление определённым ОБ, когда для выполнения ими команд всё готово. При невозможности выполнения команды из-за того, что данные не готовы, УУ заставляет ждать ОБ, пока выполнение команды будет возможным.

Таким образом, если длительность операции, задаваемой последующей командой, меньше и связь между её данными и результатами выполнения предыдущей команды отсутствует, то результат этой операции окажется в регистре раньше, чем результат операции предыдущей команды. Так в CDC-6600 новая команда поступает в каждом машинном цикле, тогда как быстродействие ОБ позволяет произвести суммирование с фиксированной точкой за три машинных цикла, умножение с плавающей точкой - за 10, а деление с плавающей точкой за 29 машинных циклов. Таким образом, для того, чтобы темп поступления команд не нарушился, должно быть предусмотрено определённое число операционных блоков соответствующих типов. Очевидно, что для различных прикладных задач, содержащих различное сочетание команд (в том числе и различный процент встречаемости разных команд в программе), эффективность применения параллельного процессора будет сильно варьироваться от задачи к задаче. Следует отметить, что принцип управления вычислительным процессом, используемый в CDC-6600, является одним из прообразов *принципов управления в потоковых машинах с управлением данными*. В таких машинах команды, для которых готовы все данные (операнды), в принципе, могут выполняться независимо от их места в программе. С другой стороны, параллельный процессор CDC-6600 является родоначальником самой современной идеологии построения *процессоров с очень длинным командным словом*.

Реализация параллельного процессора в CDC-6600 не была бы столь эффективной, если бы в нём не был применён, хоть и в зачаточном виде,

*конвейер команд*. Поэтому рассмотрим следующий способ усовершенствования скалярной обработки - конвейер команд. Конвейер команд реализует способ обработки неявных векторов. Сущность его состоит в следующем. (Следует обратить внимание на то, что конвейер команд является развитием способа предварительного просмотра команд). Последовательность выполнения каждой команды разделяется в процессоре на основные этапы:

- а) выборка команды (B);

- б) декодирование команды (D);

- в) вычисление адреса операнда (A);

- г) выборка операнда (F);

- д) выполнение операции (E);

- е) запоминание результата (Z);

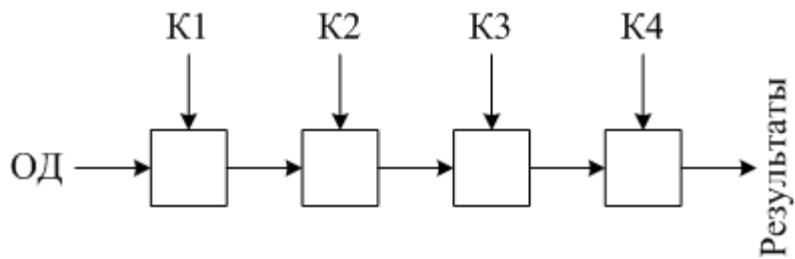

Приведённое разделение является условным, так как в каждом конкретном процессоре и число этапов, и сами этапы могут быть различными, но сама сущность последовательности выполнения команды остаётся неизменной (неймановская архитектура). Наиболее общий приём конвейеризации заключается в том, что для выполнения соответствующей этапу операции вводятся специализированные исполнительные узлы, и при этом, когда в конвейере заканчивается исполнение определенного этапа предыдущей команды, высвобождается соответствующий исполнительный узел и может быть начато выполнение аналогичного этапа следующей команды. В идеальной ситуации очередная команда должна поступать на конвейер в тот момент, когда информация предыдущей команды ушла из первого узла во второй, что определяет, в нашем случае, шестикратное повышение производительности, в случае, если все узлы выполняют свои операции за одинаковое время  $t_{\text{эт}}$  (этапа). Тогда каждая команда требует времени  $6t_{\text{эт}}$  для своего исполнения. На выходе конвейера результаты выполнения каждой из последовательности команд записываются в память через  $t_{\text{эт}}$ . Конвейер команд условно показан на рис. 2.3 ниже.

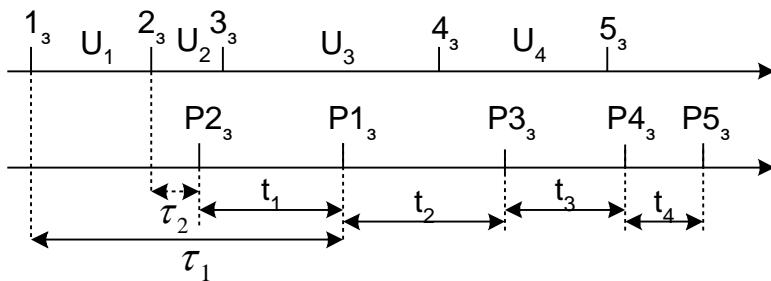

Рис. 2.3 Конвейер команд

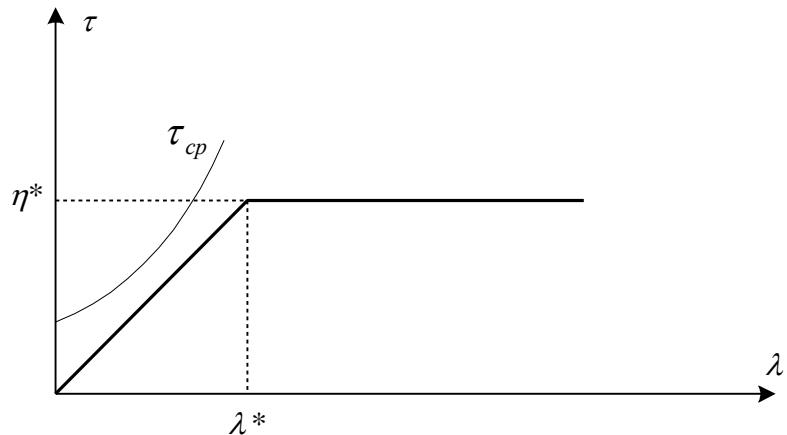

$T_{\text{латентное}}$  – время от запуска конвейера до выдачи первого результата;

$1/T_{\text{ср}}$  – интенсивности выходного потока конвейера;

$T_{\text{ср}}$  – среднее время появления результатов работы конвейера.

В табл. ниже приведены данные последовательной реализации этапов выполнения  $i$ -ой команды. При этом строки таблицы отмечены названиями

устройств или узлов, выполняющих соответствующий этап выполнения команды. Так, этапы а), г) и е) реализуются с обращением к памяти, этап б) - в устройстве управления (УУ), этап в) - в блоке вычисления адреса (БВА), д) - в АЛУ.

Таблица.2.1 Последовательная реализация этапов выполнения  $i$ -ой команды

| Узлы   | Последовательность прохождения команды по исполнительным узлам во времени |                                   |                                                |                                      |                                |                                            |  |

|--------|---------------------------------------------------------------------------|-----------------------------------|------------------------------------------------|--------------------------------------|--------------------------------|--------------------------------------------|--|

| Память | А). Выборка $i$ -ой команды из памяти                                     | $i+1$                             | $i+2$                                          | $i+3$                                | $i+4$                          | $i+5$                                      |  |

| УУ     | $i-1$                                                                     | б). Декодирование $i$ -ой команды | $i+1$                                          | $i+2$                                | $i+3$                          | $i+4$                                      |  |

| БВА    | $i-2$                                                                     | $i-1$                             | в). Вычисление адреса операнда $i$ -ой команды | $i+1$                                | $i+2$                          | $i+3$                                      |  |

| Память | $i-3$                                                                     | $i-2$                             | $i-1$                                          | г). Выборка операнда $i$ -ой команды | $i+1$                          | $i+2$                                      |  |

| АЛУ    | $i-4$                                                                     | $i-3$                             | $i-2$                                          | $i-1$                                | д). Выполнение $i$ -ой команды | $i+1$                                      |  |

| Память | $i-5$                                                                     | $i-4$                             | $i-3$                                          | $i-2$                                | $i-1$                          | е). Запоминание результата $i$ -ой команды |  |

Из рассмотрения данной таблицы видно, что при выполнении одной команды происходит три обращения к памяти. Причём для разных команд число обращений к памяти может варьироваться. Кроме того, если команды не выполняются одна за другой или не в каждой команде используются все исполнительные узлы конвейера, а также если этапы выполнения команды имеют различную продолжительность, оптимальное повышение производительности не достигается. Нарушения последовательности событий имеют место либо при выполнении команд переходов и обращения к подпрограммам, либо при переключениях контекста. В этих случаях конвейер нарушается. Конвейер нарушается и в том случае, когда результат  $i$ -ой команды используется как operand ( $i+1$ )-ой. При выполнении коротких команд некоторые узлы конвейера не используются. К тому же, одни из них работают медленнее, чем другие. Эти обстоятельства также снижают общую производительность конвейера. Подробно этот вопрос рассмотрен потому, что на определённом этапе развития вычислительной техники стали видны

проблемы, которые необходимо решать для улучшения скалярной обработки данных.

Для грубой оценки повышения производительности процессора, имеющего место в результате применения конвейера, можно принять, что самым медленным участком конвейера является узел, в котором собственно происходит выполнение операции, предписанной командой. Тогда повышение производительности в конвейере определяется в первом приближении отношением суммы средних значений времени работы всех узлов конвейера к средней величине времени работы самого медленного участка конвейера, при этом среднее берётся для заданной комбинации команд. В любом конвейере производительность определяется самым длинным участком.

Нарушение строго последовательного выполнения команд программы вызывает необходимость очистки конвейера от команд, выполнение которых началось после команды, нарушившей эту последовательность, и повторного заполнения конвейера. Доля команд, на которых естественная последовательность выполнения программы нарушается, обычно составляет 15-20% их общего количества, а вызываемое процентное снижение производительности превышает вероятность их появления в программе. Таким образом, из приведённых рассуждений видно, что основными проблемами при организации конвейера являются следующие:

- первая проблема - это уменьшение числа обращений к памяти при выполнении одной команды;

- вторая - это решение задачи разбиения цикла исполнения команды на равные по времени этапы;

- третья - это разработка механизмов, предотвращающих большие потери производительности процессора при нарушении последовательности выполнения команд.

Первая проблема в современных процессорах решается за счёт введения модульной организации памяти с применением принципа расслоения памяти, построением иерархической сверхоперативной памяти (КЭШ 1-го и 2-го уровня), выполняющей функцию буфера между процессором и оперативной памятью, разделением КЭШа на КЭШ команд и КЭШ данных. Одним из путей преодоления второй проблемы может быть уменьшение времени этапа д) собственно выполнения команды, за счёт его внутренней конвейеризации. В качестве примера рассмотрим команду умножения с плавающей точкой двух десятичных чисел  $3,8 \times 10^2$  и  $9,6 \times 10^3$ . Процессор выполняет эту операцию за три шага:

- перемножает мантиссы ( $3,8 \times 9,6 = 36,48$ );

- складывает порядки ( $2+3=5$ );

- нормализует результат, т.е. размещает в необходимом месте десятичную запятую ( $3,648 \times 10^6$ ).

Если узел, выполняющий операцию умножения с плавающей точкой, разбить на три самостоятельных узла, каждый из которых будет предназначен для выполнения одного из трёх шагов, то во время выполнения шага 3, узлы, выполняющие шаги 1 и 2 не заняты никакими действиями. Применение конвейера могло бы позволить исполнительным узлам 1 и 2 обрабатывать следующую пару чисел одновременно с выполнением шага 3 над данной парой. Данный пример характерен ещё и тем, что иллюстрирует *параллелизм на уровне операций* в команде, т.е. шаги 1 и 2 для одной команды могут выполняться параллельно на самостоятельных исполнительных узлах. То, в какой мере конвейер может ускорить работу процессора, зависит от структуры конвейера. Организация конвейера может быть предназначена и для таких операций, как пересылка данных и их извлечение из памяти, и для арифметических операций. Если какая-то операция требует сразу два или более operandов, находящихся в памяти и извлечение operand'a из памяти занимает несколько тактов, то при конвейерной организации процессор может начинать циклы обращения к элементам данных на каждом такте.

Решение третьей проблемы возможно с помощью таких приёмов, как, например, определение наиболее вероятного изменения последовательности команд при выполнении команд перехода или выполнения обеих ветвей программы. И то и другое реализуется с помощью введения специальных аппаратных средств, например, так называемого блока ветвлений и организации второго конвейера команд. Процессор с *двумя и более конвейерами команд* называется *суперскалярным процессором*.

Таким образом, мы рассмотрели этап развития скалярной обработки, который определяет обработку неявных векторов, т.е. таких, которые не связаны ни с введением в состав системы команд векторных команд, ни с введением в структуру процессора специальных схем поддержки обработки векторных данных. Этот этап завершает длительный процесс формирования структуры процессора, организация которого ориентирована на выборку operandов из памяти и занесение результатов операций в память. Такие структуры получили название "*память-память*".

Промежуточным вариантом между СОД, обладающими структурой "*память-память*" и структурой "*регистр-регистр*", является СОД, включающая в свой состав специализированные процессоры. К ним относятся матричные, векторные и ассоциативные процессоры. Суть их заключается в том, что все они предназначены для обработки явных векторов. Более подробно эти процессоры будут рассмотрены позднее. Здесь следует только отметить, что типичными представителями структуры "*регистр-регистр*" являются так называемые RISC (Reduced Instruction Set Computer) процессоры, обладающие таким сокращённым набором команд, что этап исполнения каждой из них в конвейере команд равен одному такту. В структуру таких процессоров введено большое количество регистров,

позволяющее исполнительным устройствам АЛУ работать только с регистрами.

Особенное место среди процессоров со структурой, близкой к структуре "регистр-регистр", но взявшей лучшие черты и от структуры "память-память", является процессор с очень длинным командным словом (VLIW – Very Long Instruction Word). Этот тип процессоров будет также рассмотрен позднее. Но здесь необходимо отметить следующее. Механизм, обеспечивающий реализацию VLIW, основан на *синхронном параллельном выполнении нескольких команд одной программы*.

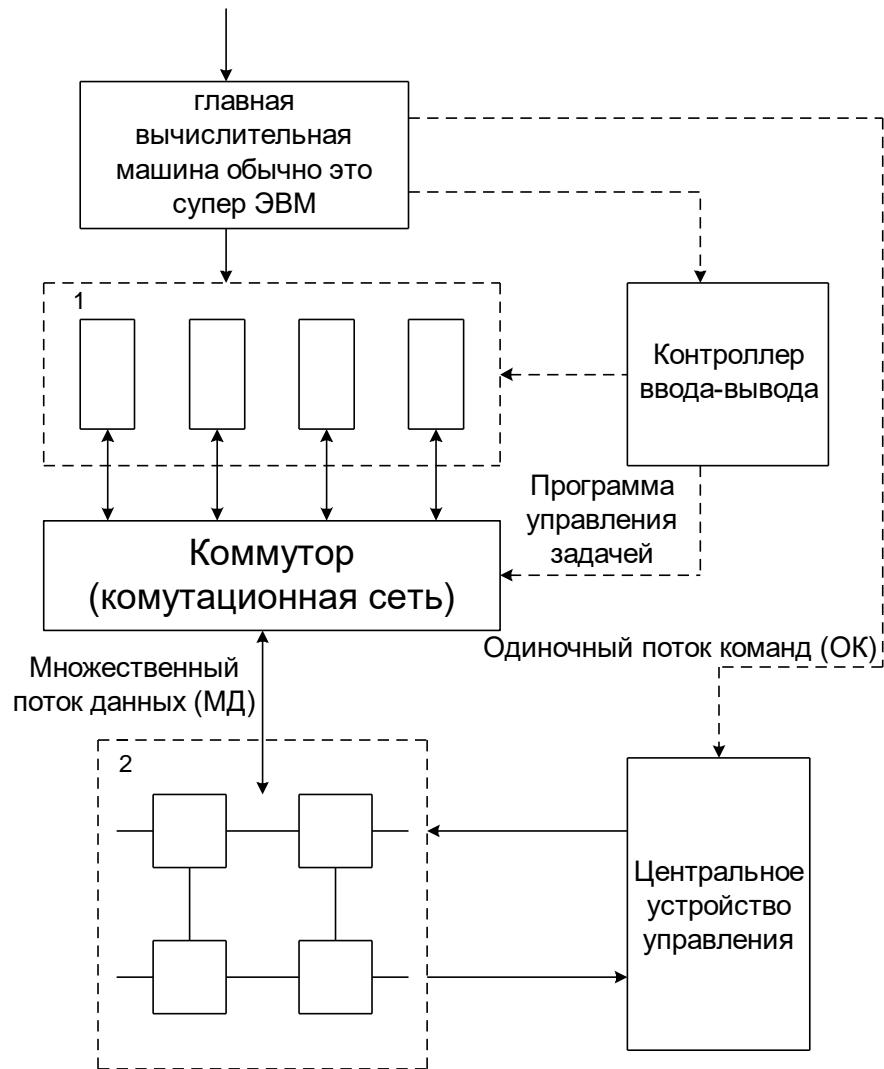

Следующим усовершенствованием обработки данных явилось введение *асинхронного параллельного выполнения независимых ветвей одной программы или разных программ* за счёт построения многопроцессорной вычислительной системы (МВС) с децентрализованным управлением вычислительным процессом. Собственно изучению МВС и посвящены основные разделы данного курса лекций. Дальнейшее развитие способов обработки данных, на мой взгляд, будет связано с появлением новых архитектурных решений, связанных как с усовершенствованием неймановской архитектуры, так и построением новых, например, такой, о которой заявил российский учёный Б.А. Бабаян.

Ниже приведена обобщённая схема эволюции способов обработки данных (см. таблицу ниже).

Таблица. 2.2 Эволюция способов обработки данных

| Вновь вводимые способы обработки данных                                                    | Механизмы их реализации                                                                                         |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Базовый вариант скалярной обработки                                                        | Централизованное управление последовательным процессом исполнения команд программы                              |

| Предварительный просмотр команд                                                            | Параллельное выполнение выборки и декодирования команды с исполнением предыдущей команды                        |

| Функциональный параллелизм                                                                 | Параллельная работа нескольких автономных исполнительных функциональных узлов                                   |

| Обработка неявных векторов                                                                 | Конвейер команд                                                                                                 |

| Суперскалярная обработка                                                                   | Несколько конвейеров команд                                                                                     |

| Обработка явных векторов                                                                   | Централизованное управление параллельным процессом исполнения векторных команд в специализированных процессорах |

| Синхронное параллельное выполнение нескольких команд одной программы                       | Очень длинное командное слово                                                                                   |

| Асинхронное параллельное выполнение независимых ветвей одной программы или разных программ | Децентрализованное управление множеством процессоров                                                            |

## Лекция 4

### 3. Уровни параллелизма при выполнении прикладных задач

Как следует из рассмотрения предыдущего материала, повышение производительности ВС базируется на идее распараллеливания вычислительных процессов [2]. При этом реализация параллельных процессов потребовала создания не только аппаратных средств многопроцессорных вычислительных машин и систем, но и соответствующего программного обеспечения: языковых средств описания параллельных процессов, соответствующих трансляторов, операционных систем и прикладных программ, о которых речь пойдёт позднее. Но все методы организации параллельных вычислений и способы их реализации основаны на существовании двух парадигм, имеющих отношение к автоматической обработке данных. Это *параллелизм данных* и *параллелизм прикладных задач*. В англоязычной литературе соответствующие термины обозначаются как *data parallel* и *message passing*. В основе использования свойств объектов обработки данных, определяемых этими парадигмами, лежит распределение вычислительной работы по имеющимся ресурсам вычислительной системы так, чтобы минимизировать время выполнения поступивших на исполнение задач.

Параллелизм данных имеет место тогда, когда по одной и той же программе должна обрабатываться некоторая совокупность данных, поступающих в систему от нескольких источников одновременно. Например, обработка информации от датчиков, измеряющих одновременно один и тот же параметр и установленных на нескольких однотипных объектах. Основная идея подхода, основанного на параллелизме данных, заключается в том, что одна операция может выполняться сразу над всеми элементами массива данных. Следовательно, различные фрагменты такого массива должны обрабатываться на различных исполнительных узлах системы.

Параллелизм прикладных задач имеет место тогда, когда прикладная задача может быть разбита на несколько относительно самостоятельных подзадач, каждая из которых может выполняться на разных процессорах параллельно над множеством, в общем случае, различных и разнотипных данных.

Рассуждая о распараллеливании вычислительных процессов, необходимо иметь в виду, что, прежде всего, должна быть возможность совмещения во времени каких-либо этапов решения задач. Степень детализации при разделении процесса решения задачи на этапы и определяет уровни параллелизма при выполнении прикладных задач. Здесь следует обратить внимание на следующее. Рассмотренные парадигмы не связаны с организацией конвейеров операций и команд, рассмотренных выше, хотя и тот и другой являются реализацией низших уровней параллелизма. Однако здесь параллелизм связан с совмещением во времени выполнения различных этапов в первом случае следующих друг за другом операций, а во втором команд, сохраняя последовательный характер обработки данных. Что же касается непосредственно распараллеливания вычислительного процесса, то можно выделить следующие уровни параллелизма. Первый - это уровень скалярных операций,

когда различные операции одновременно выполняются на различных исполнительных узлах над различными данными. Пример:

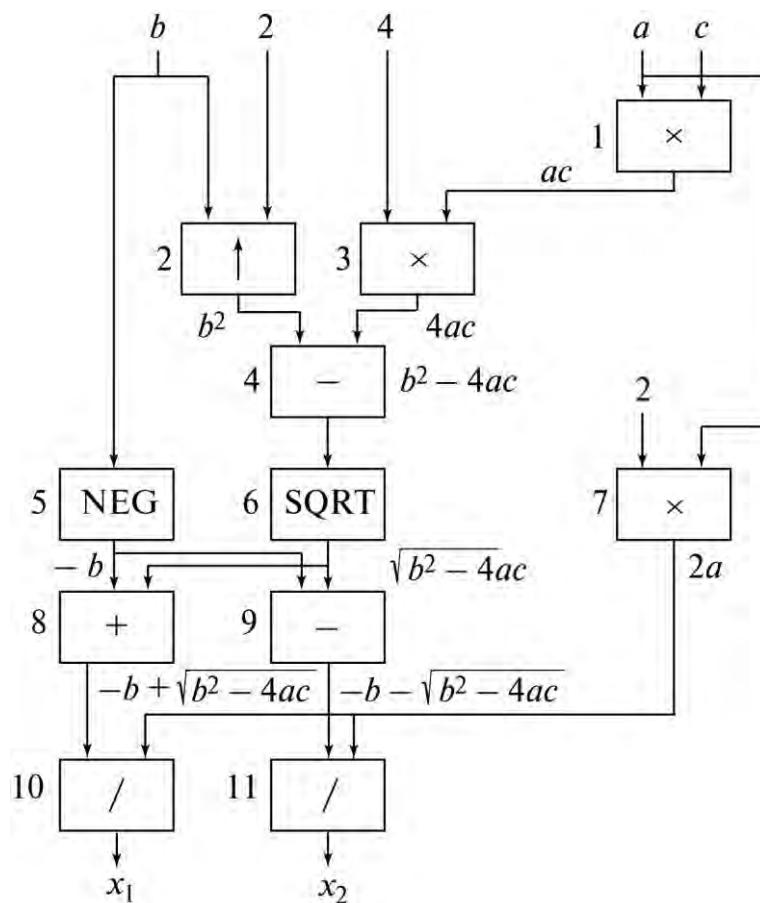

$$X_1 = \frac{-b + \sqrt{b^2 - 4ac}}{2a};$$

три операции ( $b^2$ ,  $4ac$ ,  $2a$ ) можно выполнить параллельно.

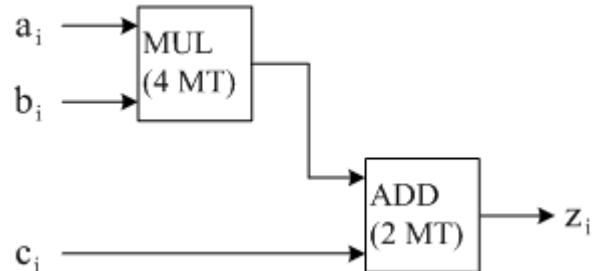

Примером процессора с таким видом параллелизма является процессор машины CDC-6600, рассмотренной выше. Второй - это *уровень векторных операций*, когда одна и та же операция одновременно выполняется на одинаковых исполнительных узлах над различными однотипными данными. Пример: усреднение яркости точек изображения (усреднение яркости двух соседних точек → усреднение яркости столбца → усреднение яркости столбцов). Уровень векторных операций причислен к более высокому уровню потому, что изначально в одной векторной команде предусматривается выполнение множества одинаковых операций. Процессоры, предназначенные для реализации такого уровня параллелизма, называются *векторными процессорами*. Следует отметить, что для удешевления построения векторного процессора выполнение векторных операций, инициированных одной векторной командой, может происходить на одном исполнительном узле, реализующим принцип конвейера операций. Примером таких процессоров являются процессоры фирмы CRAY Research. Процессоры, в которых введены по четыре одинаковых исполнительных узла, способных одновременно выполнять по четыре одинаковых операций одной векторной команды, применены фирмой NEC в суперЭВМ семейства SX.

Одним из наиболее распространённых типов параллелизма в обработке информации является параллелизм на *уровне независимых ветвей (подзадач)* *прикладной задачи*. Прежде чем подробнее остановиться на этом уровне параллелизма, отметим, что существует более высокий уровень - *уровень естественного параллелизма независимых задач*. Реализация этого уровня базируется на предположении о том, что в ВС поступает непрерывный поток не связанных между собой задач, решение которых не зависит от результатов решения других задач. Наличие же в ВС нескольких модулей обработки данных, например, процессоров, позволяет практически совмещать во времени выполнение таких задач. Поскольку этот уровень не требует более подробных комментариев, отметим, что мы ввели понятия 4-х уровней параллелизма, а теперь вернёмся к пояснению уровня параллелизма независимых ветвей прикладной задачи.

Двумя *независимыми ветвями* одной программы будем считать такие её части, при выполнении которых выполняются следующие условия:

- ни одна из входных для ветви программы величин не является выходной величиной другой ветви программы (отсутствие функциональных связей);

- для обеих ветвей программы не должна производиться запись данных в одни и те же ячейки памяти (отсутствие связи по использованию одних и тех же ячеек оперативной памяти);

- условия выполнения одной ветви не зависят от результатов или признаков, полученных при выполнении другой ветви (независимость по управлению);

- обе ветви не должны использовать одни и те же стандартные подпрограммы (программная независимость).

Следовательно, такие ветви одной программы при наличии в ВС нескольких процессоров могут выполняться параллельно и независимо друг от друга.

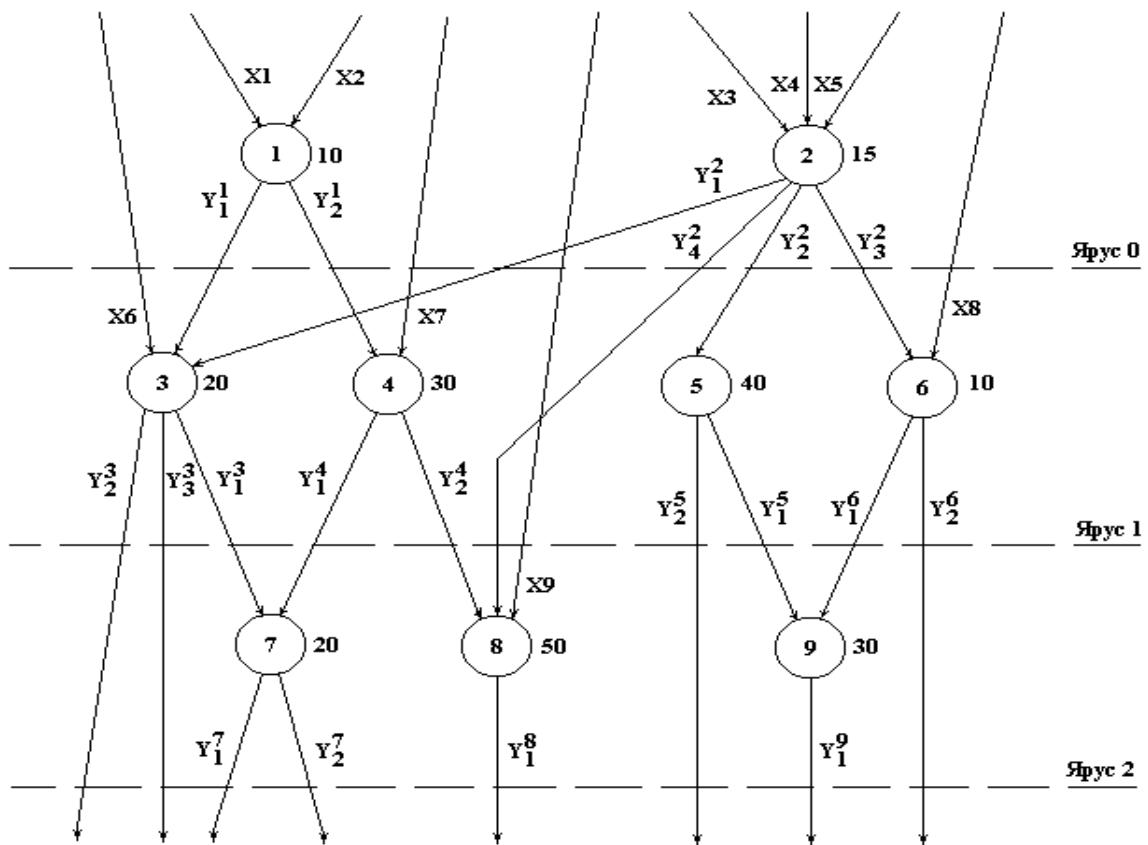

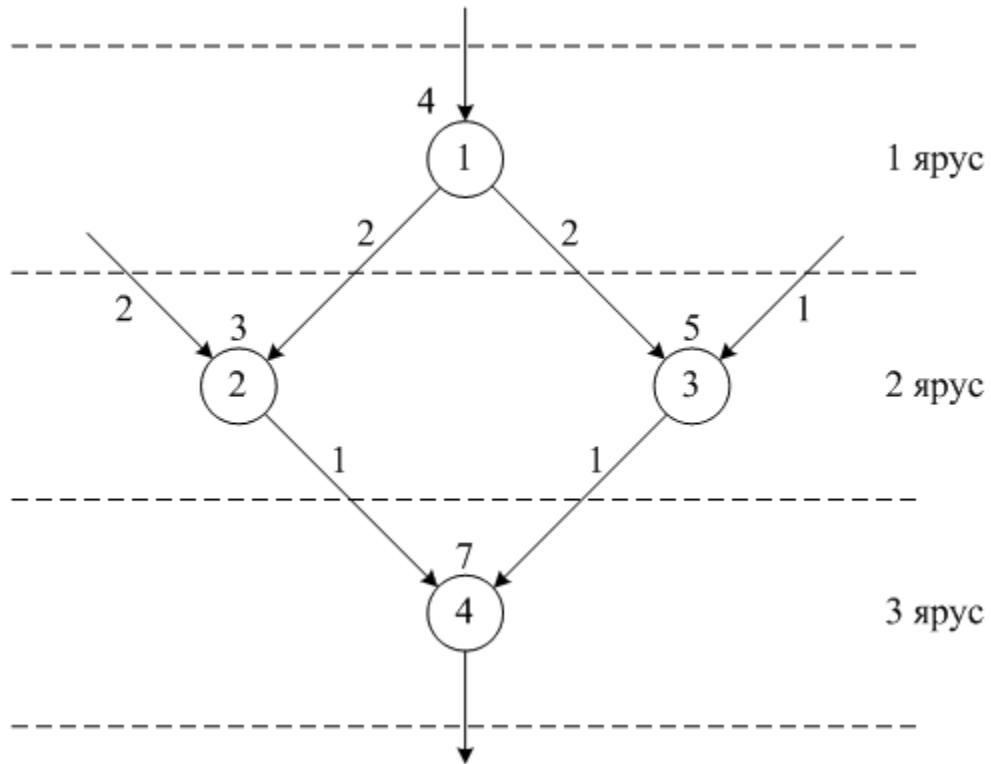

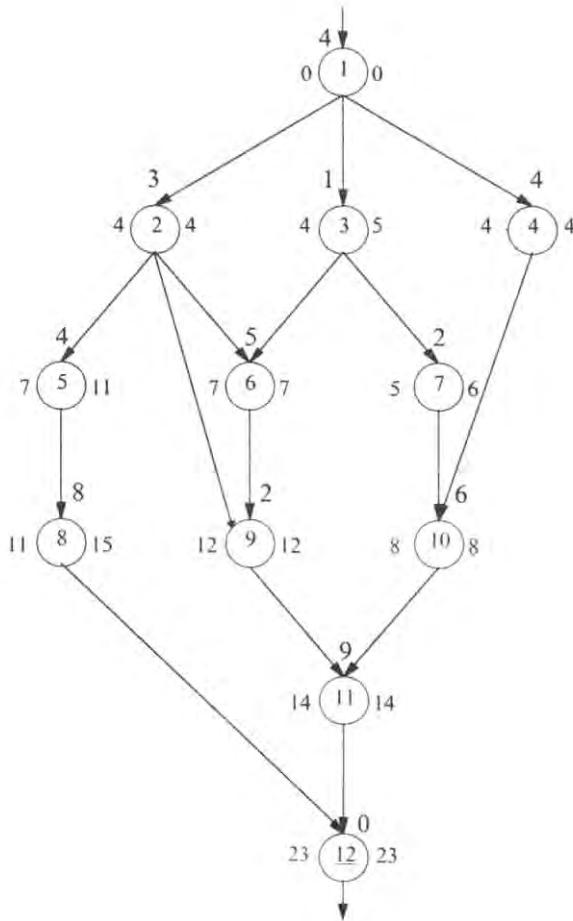

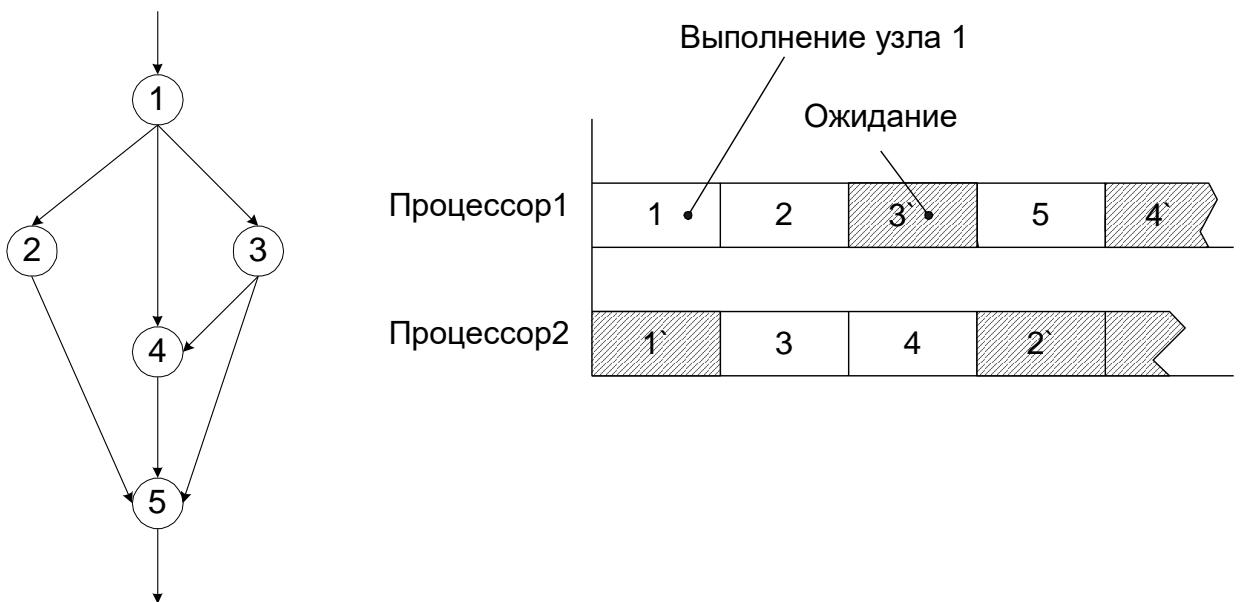

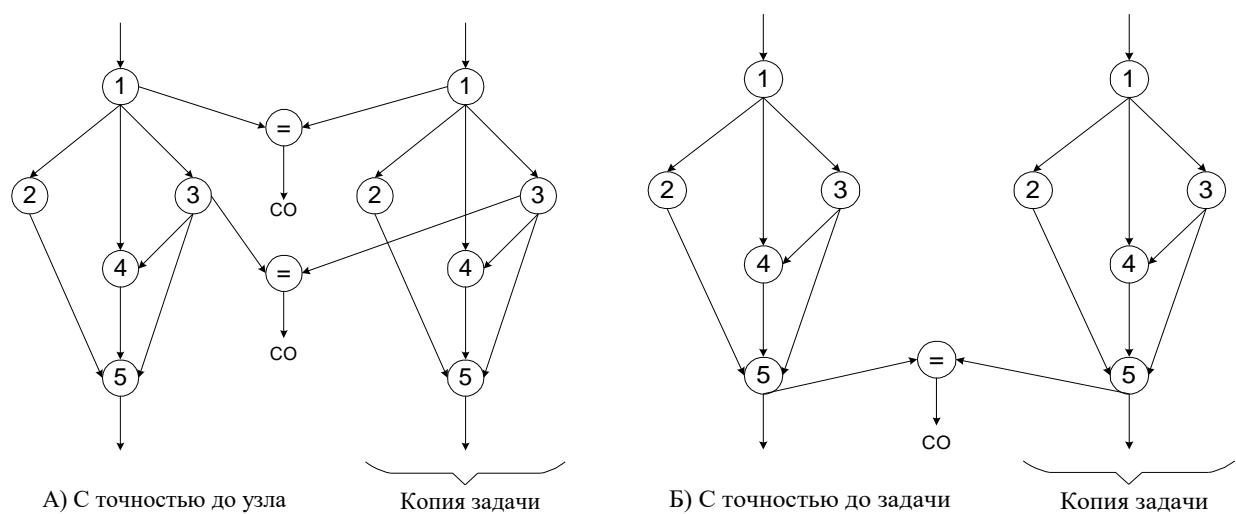

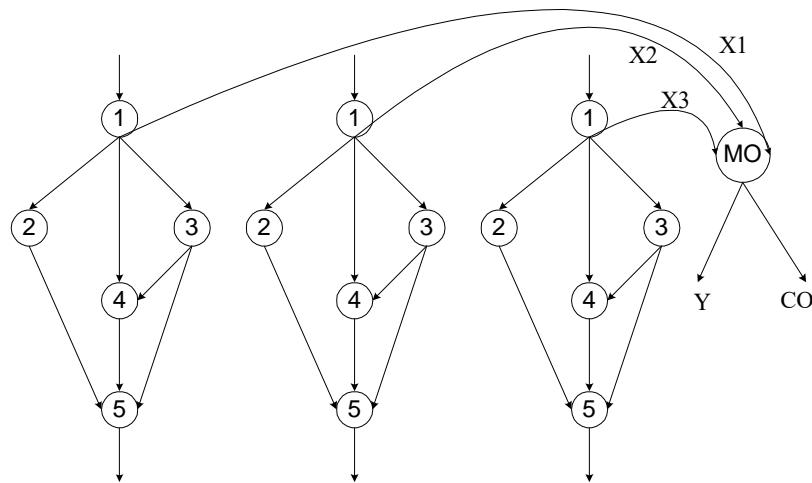

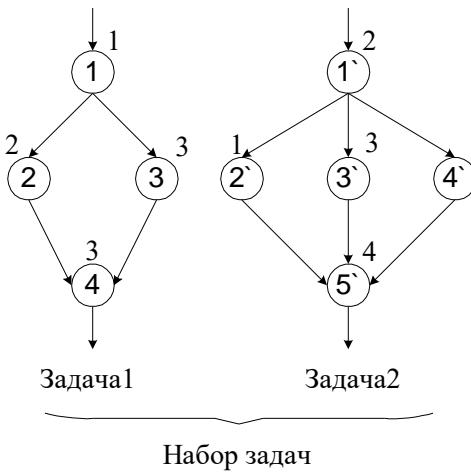

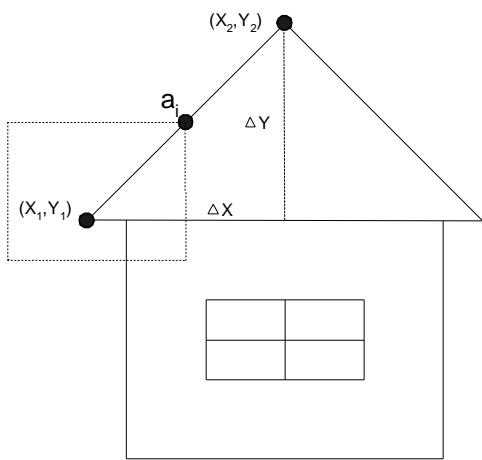

Хорошее представление о параллелизме независимых ветвей даёт ярусно-параллельная форма (ЯПФ) представления программы, которая обеспечивает возможность, используя формальное представление с помощью соответствующего языка параллельного программирования, автоматизировать процесс распараллеливания задачи. На рис. 3.1 приведён пример представления части программы в ЯПФ.

Кружками с цифрами внутри обозначены ветви (цифра - порядковый номер ветви). Длина ветви представляется цифрой, стоящей около кружка, и может соответствовать числу временных единиц, которые требуются для её исполнения (например, число машинных тактов). Стрелками показаны входные данные и результаты обработки. Входные данные обозначаются символом X, нижние цифровые индексы которых соответствуют номеру входных величин. Выходные данные обозначаются символом Y, верхний цифровой индекс которых соответствует номеру ветви, при выполнении которой получен данный результат, а нижний индекс означает порядковый номер результата, полученного при реализации данной ветви программы. Изображённая на рисунке программа содержит 9 ветвей, расположенных на трёх ярусах. Очевидно, что для ветвей каждого яруса выполняется первое условие независимости. Допустим, что выполняются и остальные три условия независимости ветвей (на графике для простоты изложения отсутствуют связи по памяти, управлению и подпрограммам). Тогда можно считать, что ветви одного яруса являются независимыми и, следовательно, есть принципиальная возможность при наличии в ВС нескольких процессоров, организовать параллельные вычисления. При этом возникает следующая задача. Анализируя рисунок ниже, можно получить результат – суммарное время выполнения программы на одном процессоре равно 255 единицам времени. Если система содержит n процессоров, то необходимо так распределить ветви программы, чтобы общее время решения программы было оптимальным. При этом предполагается, что любая ветвь может выполняться только тогда, когда для неё готовы все входные данные (следует отметить, что мы здесь не учитываем такой фактор, как объём передаваемых данных от одной ветви к другой, который может внести корректиры в полученный результат распределения ветвей по процессорам).

Рис.3.1 Представление программы в ярусно-параллельной форме

Допустим,  $n=2$ , тогда одним из решений может быть следующее. Первый процессор выполняет последовательно ветви 1-4-5-9 и тратит на это 110 единиц времени. Второй процессор выполняет 2-3-6-8-7 ветви и тратит 115 единиц времени. Таким образом, все ветви программы выполняются в целом за 115 единиц времени. Очевидно, что решений распределения будет несколько, а эффективность реализации любого распределения определяется в том числе точностью сведений о длине ветви (обычно известна приближённая её оценка) и имеющейся в ВС процедурой автоматического выбора пути решения задачи и слежения за выполнением всех её ветвей. Заметим, что практически никогда не удается избежать некоторых простоеов процессоров, которые возникают из-за отсутствия исходных данных для выполнения той или иной ветви, а это ведёт к уменьшению производительности ВС с параллельной обработкой на уровне ветвей задачи. Ещё один вывод, который можно сделать из рассмотрения данного материала, состоит в том, что с одной стороны выделить независимые ветви программ при их разработке достаточно сложно, а с другой стороны в языках программирования должны присутствовать специальные средства, отображающие параллелизм независимых ветвей программы.

При рассмотрении параллельной обработки на всех уровнях параллелизма всегда следует иметь в виду, что любая программа по своей сути является совокупностью двух частей - последовательной и параллельной. Поэтому, если, например, программа состоит из последовательной части, со-

держащей S блоков, и параллельной части, содержащей N блоков, причём каждый из последовательных блоков выполняется за время  $T_i$ , а параллельные блоки выполняются за одинаковое время  $T_n$ , то общее время выполнения программы будет

$$T = T_s + N * T_n,$$

где  $T_s$ -суммарное время выполнения последовательных частей программы.

Тогда возможный уровень параллелизма программы можно определить из выражения

$$P = N * T_n / (T_s + N * T_n).$$

Таким образом, если параллельная программа выполняется на M процессорах, то коэффициент ускорения параллельной обработки равен

$$K_u = (T_s + N * T_n) / (T_s + N * T_n / M).$$

Из этой формулы видно, что даже при  $M=N$ , эффективность параллельной обработки определяется долей последовательной части программы.

Какое максимально возможное значение коэффициента ускорения можно получить, выполняя программу на M процессорах, даёт так называемый закон Амдала, в соответствии с которым

$$K_u < 1 / (f + (1-f)/M),$$

где f-доля операций в программе, которые нужно выполнять последовательно (при этом доля понимается не по статическому числу строк кода, а по числу операций в процессе выполнения); (1-f)-доля операций в программе, которые можно выполнить параллельно.

Крайние случаи в значениях f соответствуют полностью параллельным ( $f=0$ ) и полностью последовательным ( $f=1$ ) программам. Если для конкретной программы, например,  $f=0.1$ , то ускорения более, чем в 10 раз получить в принципе невозможно вне зависимости от числа процессоров, реализующих параллельную часть. Следовательно, при формировании алгоритма параллельной программы, необходимо самое серьёзное внимание уделять поиску путей *распараллеливания последовательной части программы*.

#### 4. Распараллеливание последовательных частей программ

Преобразование последовательной части программы в параллельную форму базируется на следующем [6]. Пусть операции алгоритма разбиваются на группы, упорядоченные таким образом, что каждая операция любой группы зависит либо от начальных данных алгоритма, либо от результатов выполнения операций, находящихся в предыдущих группах. Следовательно, все операции одной группы должны быть независимыми и обладать возможностью быть выполненными одновременно на имеющихся в системе функциональных узлах. Представление алгоритма в таком виде и является *параллельной формой алгоритма*. Тогда каждая группа операций в ней называется *ярусом параллельной формы*, число групп - *высотой параллельной формы*, максимальное число операций в ярусе - *шириной параллельной формы*.

Рассмотрим три уровня представления последовательных программ, на которых их распараллеливание даёт существенный выигрыш в производительности вычислительной системы. (Будем считать, что уровень независимых ветвей задачи с одной стороны рассмотрен выше, а с другой стороны он, в большинстве случаев, и определяет параллельную часть программы). Итак, первый уровень основан на том, что программа разбивается на относительно небольшие участки, достаточно тесно связанные между собой как по данным так и по управлению, и среди них выделяются те, которые могут быть выполнены параллельно. Реализации таких участков на ВС называются *процессами*. Для определения таких процессов строится граф потока данных, анализируются множества входных (считываемых) переменных R(read) и выходных (записываемых) переменных W(write) каждого процесса. Два процесса  $i$  и  $j$  могут выполняться параллельно при следующих условиях:

$$R_i \wedge W_j = 0$$

$$W_i \wedge R_j = 0$$

$$W_j \wedge W_i = 0$$

Это означает, что входные данные одного процесса не должны модифицироваться другим процессом и никакие два процесса не должны модифицировать общие переменные.

Второй уровень связан с распараллеливанием циклов. Границы циклов находятся по формальным признакам описания циклов в соответствующих языках программирования. Процесс преобразования последовательного цикла для параллельного выполнения заключается в том, что из переменных формируются векторы, над которыми выполняются векторные операции. Поскольку векторные операции выполняются параллельно над всеми или частью элементов вектора (в зависимости от вычислительных ресурсов ВС), то происходит значительное ускорение вычислительного процесса.

Третий уровень - это распараллеливание линейных участков. *Линейным участком* программы назовём часть программы, операторы которой выполняются в естественном порядке или порядке, определённом командами безусловных переходов. Линейный участок ограничен начальным и конечным операторами.

*Начальным оператором* линейного участка назовём оператор, для которого выполняется по крайней мере одно из следующих условий:

- у оператора не один непосредственный предшественник;

- у непосредственного предшественника более одного непосредственного последователя.

*Конечным оператором* линейного участка назовём оператор, для которого выполняется по крайней мере одно из следующих условий:

- у оператора не один непосредственный последователь;

- у непосредственного последователя оператора больше одного непосредственного предшественника.

Исходя из этих определений, легко построить алгоритм нахождения линейных участков программы. Внутри линейного участка распараллеливание может производиться по операторам, а внутри операторов - распараллеливание арифметических выражений. Распараллеливание по операторам позволяет при наличии вычислительных ресурсов выполнять сразу несколько операторов.

Рассмотрим несколько примеров распараллеливания линейных участков:

### 1. Уменьшение высоты арифметических выражений:

Пусть необходимо вычислить произведение восьми чисел -  $a_1, a_2, a_3, a_4, a_5, a_6, a_7, a_8$ . Обычная схема, реализующая процесс последовательного умножения, выглядит следующим образом:

ярус 1  $a_1a_2$

ярус 2  $(a_1a_2)a_3$

ярус 3  $(a_1a_2a_3)a_4$

ярус 4  $(a_1a_2a_3a_4)a_5$

ярус 5  $(a_1a_2a_3a_4a_5)a_6$

ярус 6  $(a_1a_2a_3a_4a_5a_6)a_7$

ярус 7  $(a_1a_2a_3a_4a_5a_6a_7)a_8$

Характеристики этого дерева: высота - 7, ширина - 1. В процессе реализации сложного выражения, возможны преобразования, дающие различную параллельную сложность. Среди них нужно найти алгоритмы с наименьшей высотой. Это главная проблема этих преобразований. Если процессоров несколько, то можно предложить такой вариант уменьшения высоты приведенного дерева:

ярус 1  $a_1a_2 a_3a_4 a_5a_6 a_7a_8$

ярус 2  $(a_1a_2)(a_3a_4) (a_5a_6)(a_7a_8)$

ярус 3  $(a_1a_2a_3a_4)(a_5a_6a_7a_8)$

Характеристики этого дерева: высота - 3, ширина - 4. Таким образом, при использовании четырёх процессоров высота дерева уменьшилась на 4 яруса и, следовательно, время выполнения алгоритма сократилось более чем в два раза.

В общем случае при произвольном числе сомножителей  $n$ , высота параллельной формы равна целой части  $\log n$ . Эта параллельная форма реализуется на  $n/2$  процессорах, но в ней загруженность процессоров уменьшается от яруса к ярусу. Рассмотренный процесс перемножения чисел называется процессом сдваивания (схема сдваивания).

При вычислении произведения  $n$  чисел часто требуется знать не только конечный результат, но и все частичные произведения. В этом случае иногда авторы (Трахтенгерц Э.А.) предлагают следующую процедуру вычислений:

ярус 1  $a_1a_2 a_3a_4 a_5a_6 a_7a_8$

ярус 2  $(a_1a_2)a_3 (a_1a_2)(a_3a_4) (a_5a_6)a_7 (a_5a_6)(a_7a_8)$

ярус 3  $(a_1a_2a_3a_4)a_5 (a_1a_2a_3a_4)(a_5a_6) (a_1a_2a_3a_4)(a_5a_6a_7) (a_1a_2a_3a_4)(a_5a_6a_7a_8)$

Как легко заметить, у этого дерева: высота - 3, ширина - 4, а все процессоры на всех ярусах полностью заняты. Однако, следует обратить внимание на то, что на втором и третьем ярусах различные процессоры используют одни и те же результаты предыдущего яруса. Это означает, что данные одновременно должны быть переданы с одного процессора нескольким другим процессорам при реализации алгоритма на ВС с распределённой памятью. При реализации алгоритма на ВС с общей памятью, необходимо сначала результаты вычислений записать в общую память, а затем последовательно считать их процессорами, которые в них нуждаются. Следовательно, с одной стороны число ярусов дерева остаётся неизменным - 3, но время на выполнение ярусов увеличивается.

Следует отметить ещё один момент. В силу ассоциативности операций и последовательный, и параллельный алгоритмы дают одинаковые результаты только в условиях точных вычислений, но они будут давать разные результаты в условиях влияния ошибок округления. В этом случае считается, что устойчивость параллельных алгоритмов при большом числе процессоров оказывается хуже устойчивости последовательных алгоритмов.

## 2. Преобразование линейных рекурентных выражений:

Рассмотрим блок операторов:

$$X = BCD + E$$

$$Y = AX$$

$$Z = X + FG$$

При использовании одного процессора этот блок может быть вычислен за 6 шагов, если один временной шаг отводится для каждой арифметической операции. Путём замены операторов можно получить следующий блок:

$$X = BCD + E$$

$$Y = ABCD + AE$$

$$Z = BCD + E + FG$$

Таким образом, если ВС обладает множеством свободных процессоров, таким, что первый оператор выполняется на автономном процессоре и тогда ему необходимо 3 шага, второй и третий операторы выполняются каждый на двух, параллельно действующих процессорах, и тогда они также выполняются каждый за 3 шага. Следовательно, весь блок операторов выполнится за 3 шага на пяти процессорах с коэффициентом ускорения равным 2.

## 3. Алгоритм компактного размещения данных:

Допустим необходимо  $L$  разрядов из каждого элемента массива  $A(i)$  плотно упаковать по элементам массива  $B(j)$ . Элементы массивов представлены 64-разрядными словами, а  $L < 64$ . Если очередная секция из  $L$  разрядов целиком не помещается в очередном элементе  $B(j)$ , то оставшаяся часть должна быть перенесена в следующий элемент  $B(j+1)$ . Последовательный алгоритм упаковки очевиден. Параллельный же можно представить следующим образом. Вычисляется периодичность секций из  $L$  разрядов, полностью

заполняющих все разряды последовательных элементов массива  $B(j)$  и определяется число этих заполненных элементов. Например,  $L=48$ , тогда каждые 4 секции из  $L$  разрядов будут без остатка заполнять 3 элемента массива  $B(j)$ . В этом случае каждые 4 секции можно параллельно размещать в последовательные 3 элемента массива  $B(j)$ .

## Лекция 5

### 5. Оценка производительности ВС

В начале проектирования любой сложной системы разработчики пытаются выделить основное свойство системы, которое необходимо обеспечить в результате её создания. Таким свойством является полное соответствие системы своему назначению.

Степень соответствия системы своему назначению называется *эффективностью* системы. Обычно эффективность не удаётся определить одной величиной, и поэтому её представляют набором величин, называемых *характеристиками* системы. Естественно, этот набор должен наиболее полно отображать основное свойство системы. Если это свойство мы определим, как способность системы выполнять заданные функции, сохраняя во времени значения своих параметров в заданных пределах, то основными характеристиками системы должны быть следующие:

- производительность

- надёжность

- стоимость

Для того чтобы характеристику, а, следовательно, и эффективность системы оценить количественно, вводится понятие *показателя характеристики*. С точки зрения оценки эффективности вычислительных систем, её показатели определяются параметрами системы, в качестве которых выступают величины определяющие, например, число процессоров, ёмкость памяти, быстродействие основных компонент ВС.

Таким образом, последовательность объектов, с помощью которых осуществляется оценка эффективности ВС, может быть представлена следующим образом:

свойство – характеристика – показатель – параметр

Как было уже определено выше, производительность это характеристика вычислительной мощности системы, определяющая количество вычислительной работы, выполняемой системой в единицу времени (другими словами, количество прикладных задач, выполненных системой в единицу времени). В настоящее время существует большое количество различных способов, методов и методик оценки производительности ВС и это связано не только с существованием огромного количества видов ВС, но и с тем, что производительность определяется большим числом параметров, как самой вычислительной системы, так и прикладных задач. Поэтому существует довольно сложная проблема выделения частных показателей производительности ВС и параметров, оказывающих наиболее сильное влияние на значения этих показателей.

Среди частных показателей можно отметить следующие:

- *номинальная производительность*

- *комплексная производительность*

- *системная производительность.*

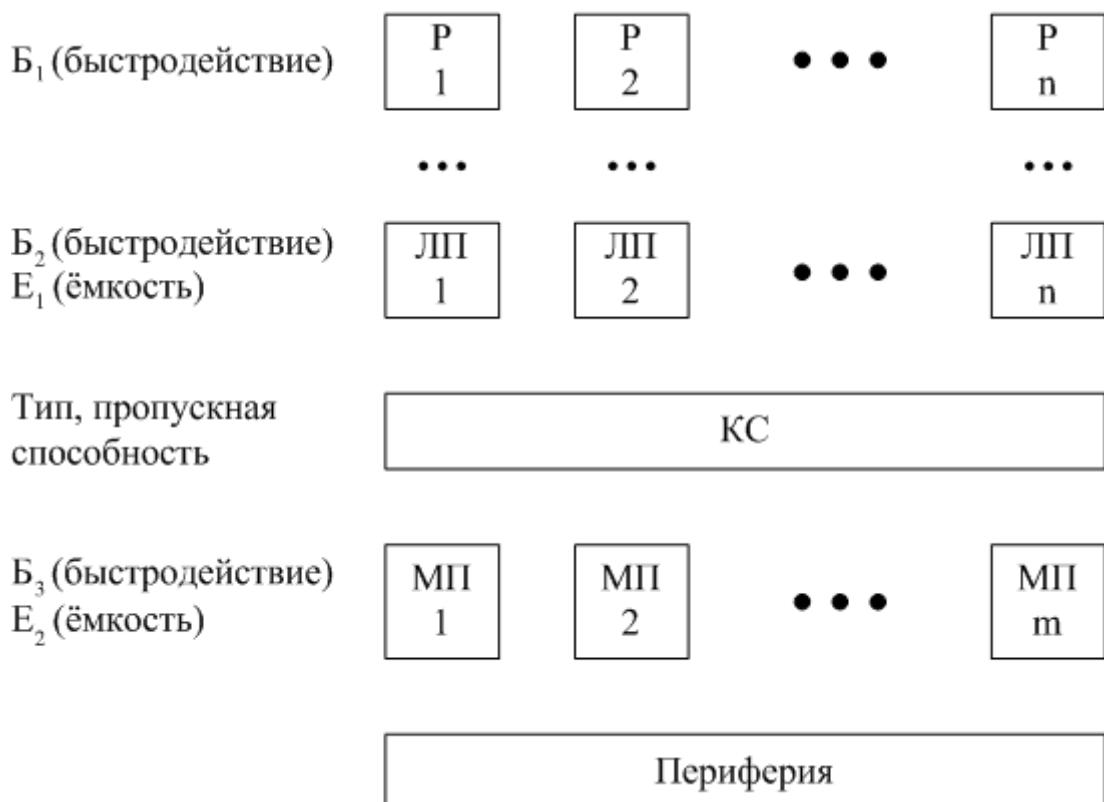

*Номинальную производительность (НП)* ВС можно определить как совокупность таких параметров системы как быстродействия устройств, входящих в её состав (процессора, памяти, канала обмена):

$$НП = \{Б_{ПР}, Б_П, Б_К\}, \text{ где}$$

$Б_{ПР}$  - быстродействие процессора

$Б_П$  - быстродействие памяти

$Б_К$  - быстродействие системы коммутации

Например, если  $Б_{ПР}=2\text{ГГц}$ ,  $Б_К=133\text{МГц}$ , то Pentium 4 будет работать как Pentium II.

Таким образом, номинальная производительность характеризует только потенциальные возможности вычислительной системы, которые не могут быть достигнуты в реальной обстановке решения конкретной прикладной задачи. Следует отметить, что довольно часто номинальная производительность оценивается только одним параметром - быстродействием основного элемента системы - процессора, а в случае нескольких процессоров - суммарным их быстродействием.

Для того, чтобы оценить влияние на производительность таких факторов как конфликты при обращении процессора к памяти, каналам ввода-вывода и другим общим ресурсам системы, используется другой показатель - *комплексная производительность (КП)*. Комплексная производительность, так же как и НП определяется совокупностью тех же параметров, однако, их значения вычисляются как произведения значений быстродействий в формуле для НП на некоторые коэффициенты  $K_i$ , принимающие значения меньшие единицы:

$$КП = \{Б_{ПР} \cdot K_1, Б_П \cdot K_2, Б_К \cdot K_3\}, \text{ где}$$

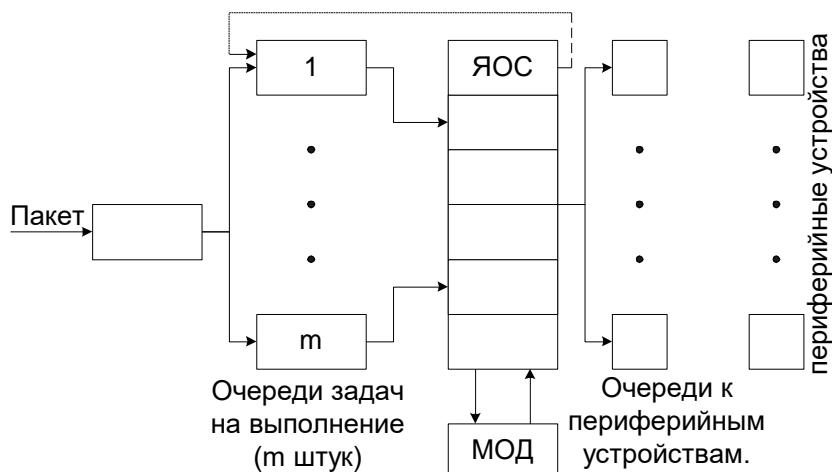

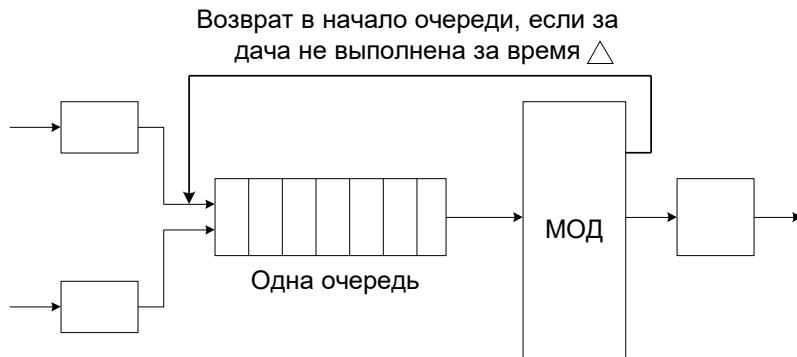

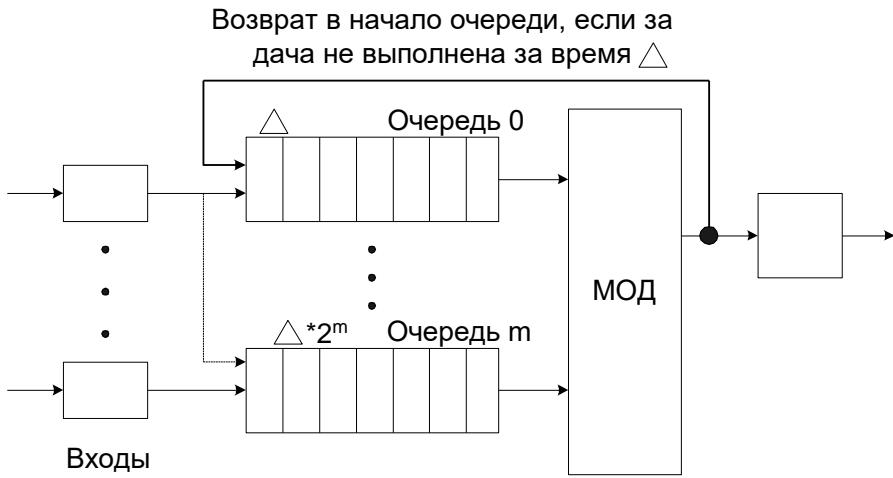

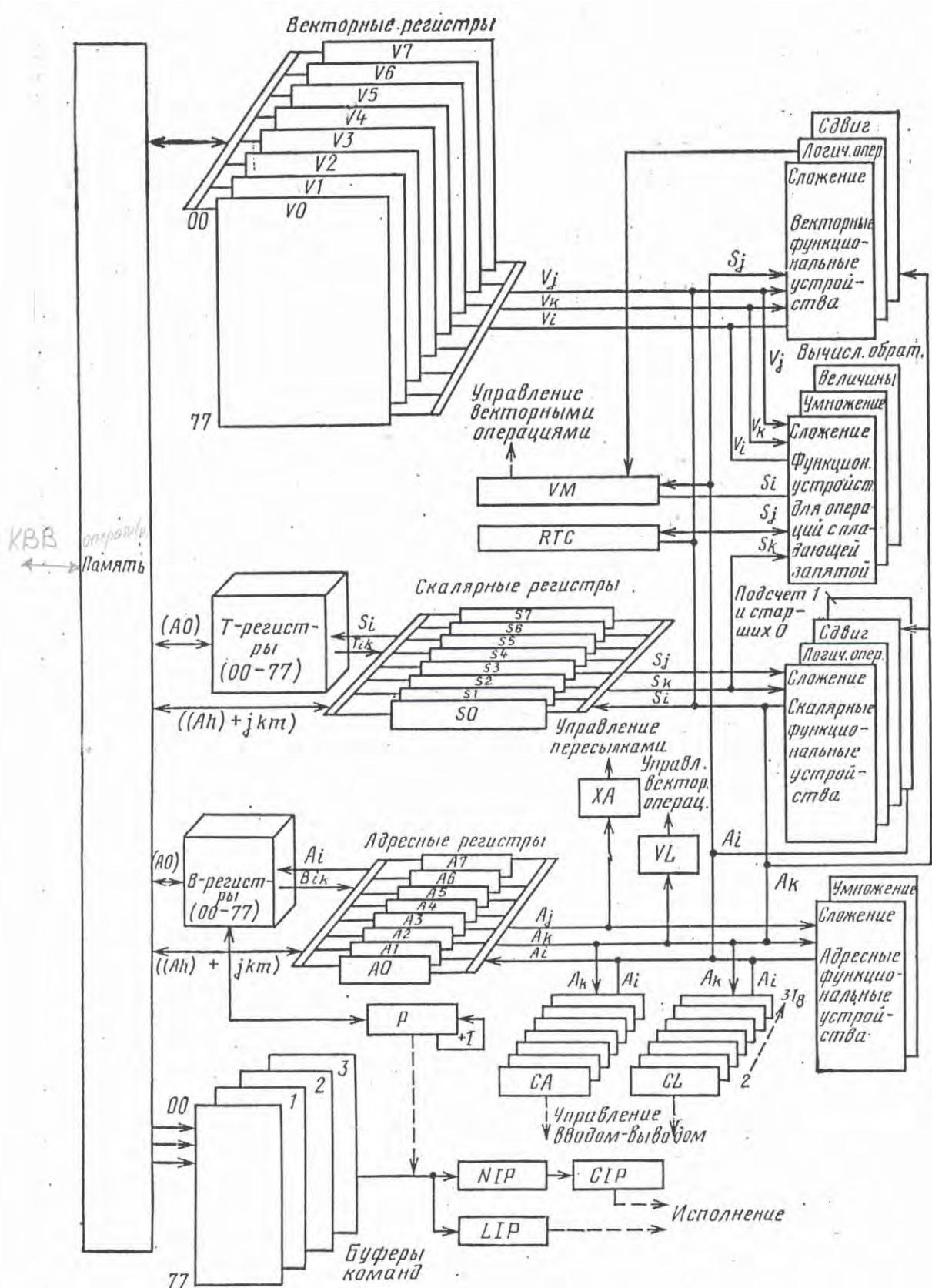

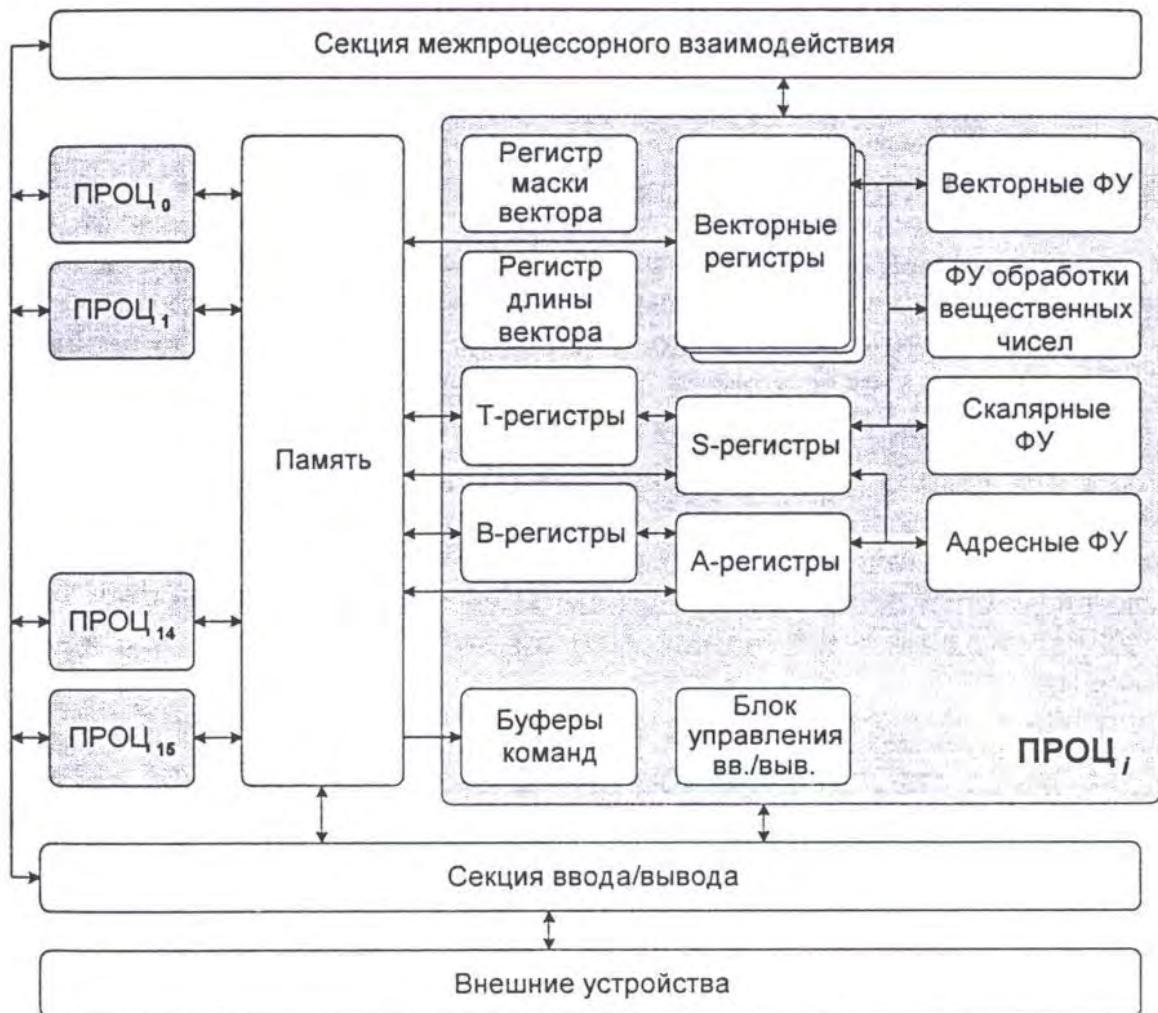

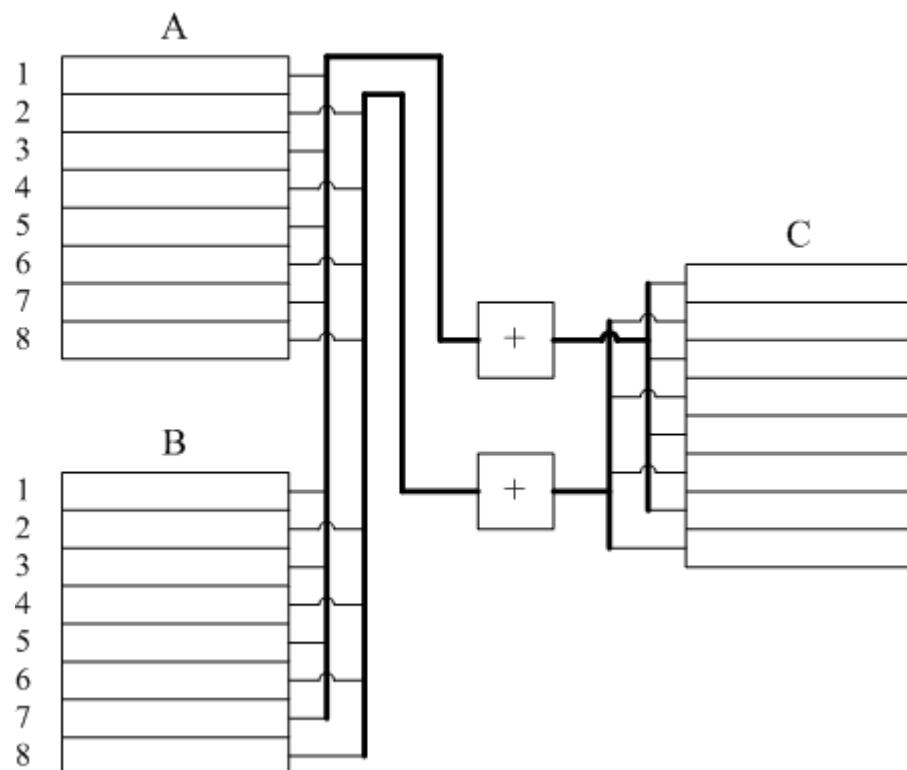

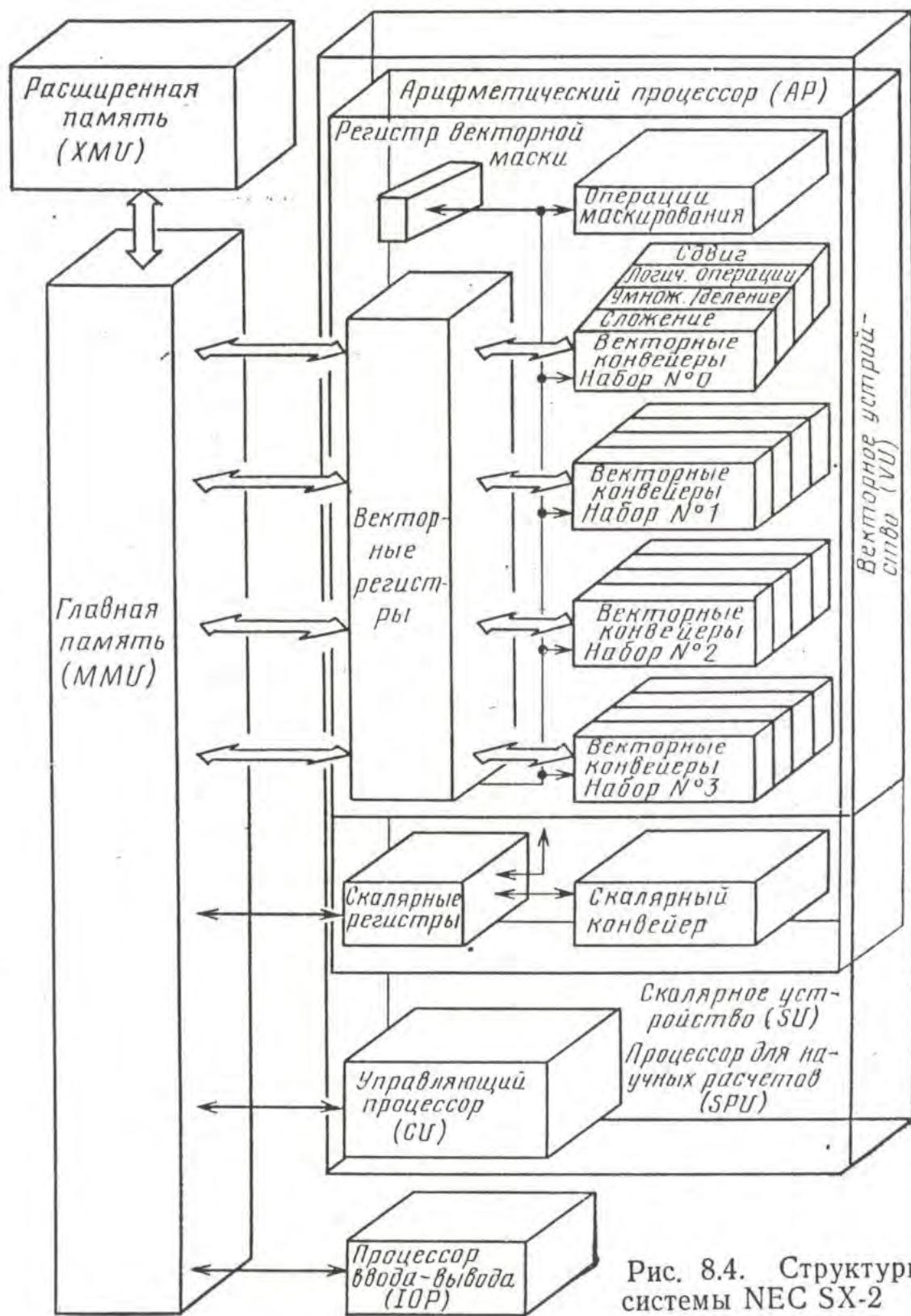

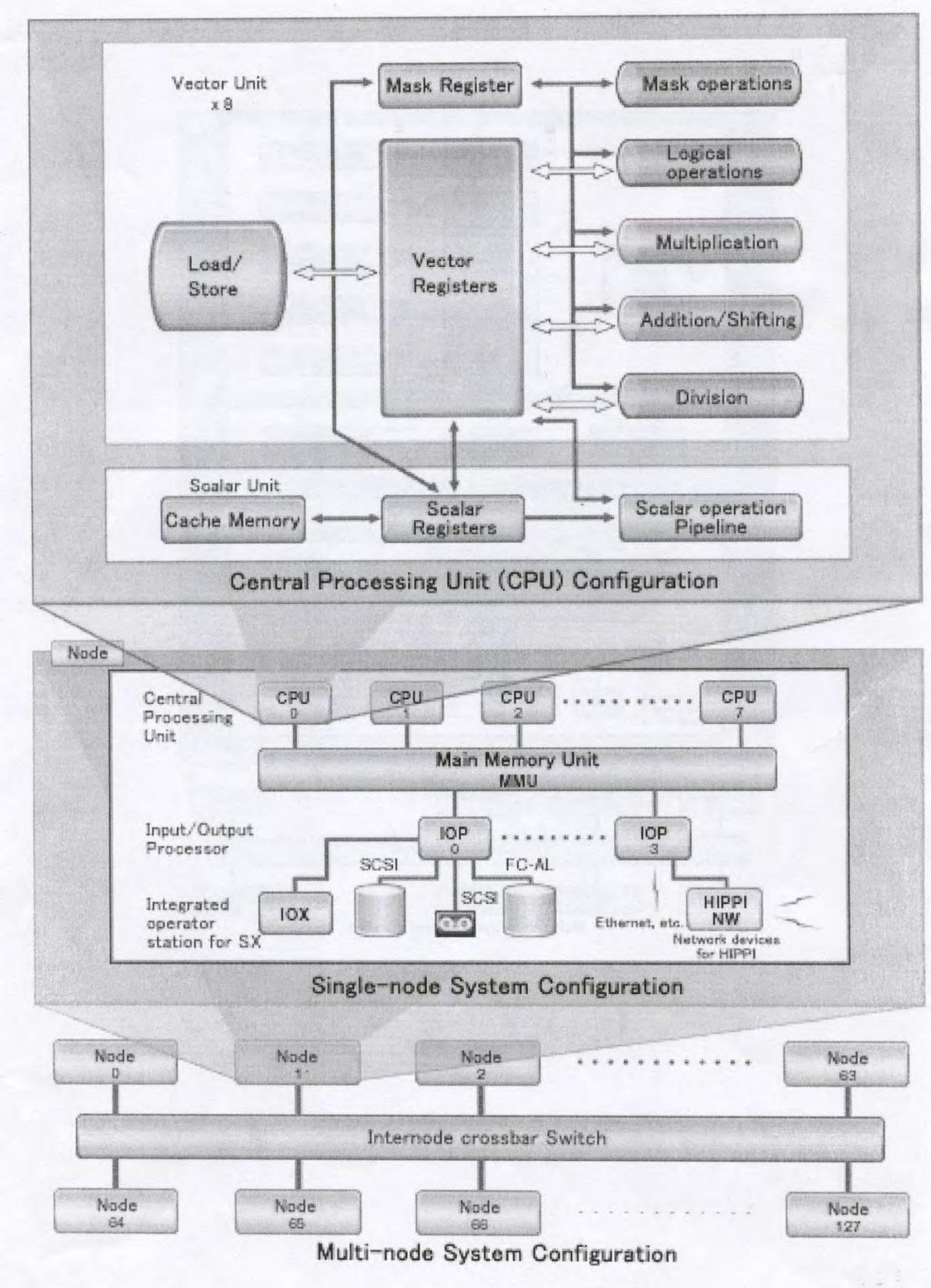

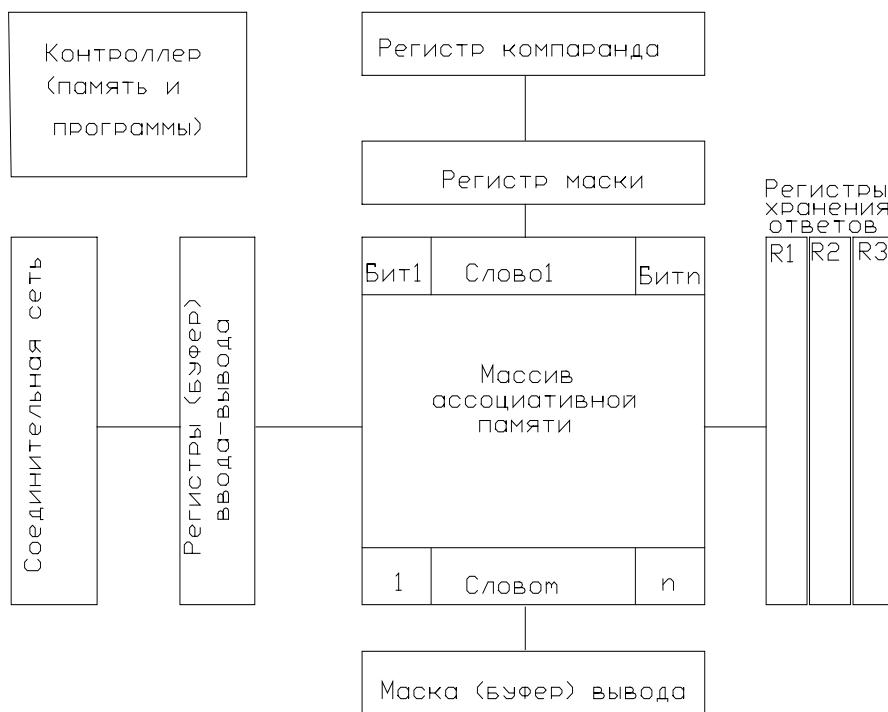

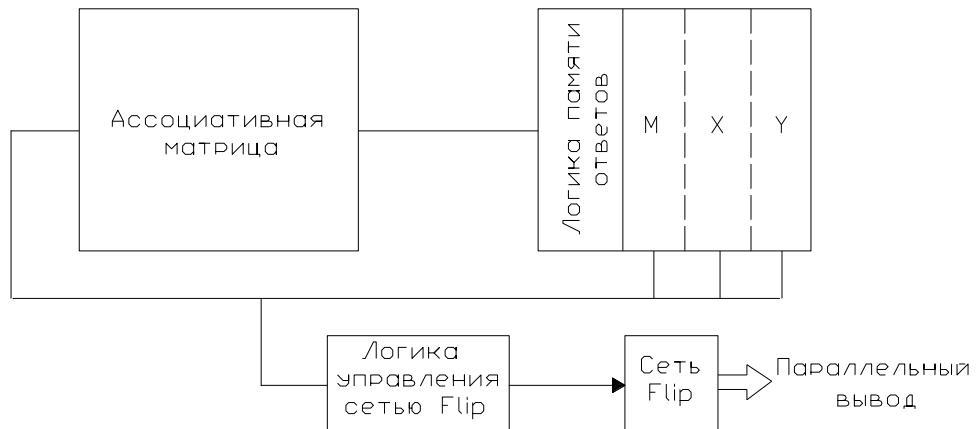

$K_1$  - коэффициент, указывающий на простой процессора из-за конфликтов при обращении к разделяемым ресурсам,