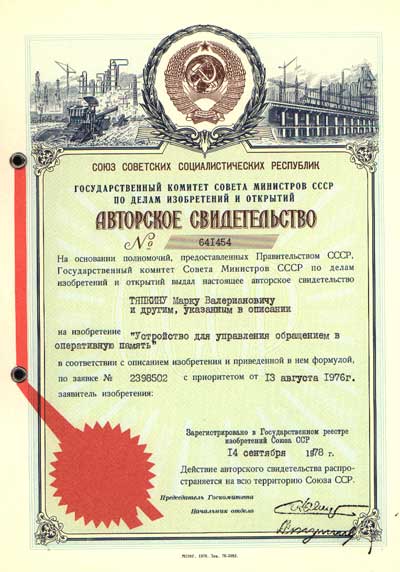

Устройство для управления обращением в оперативную память

Описание изобретения к авторскому свидетельству

Авторы изобретения: М. В; Тяпкин, В. С. Новизенцев, Б. Н. Сухих и О. Н. Сердюкова

Изобретение относится к вычислительной технике и может быть использовано для организации управления обращением к оперативной памяти (ОП) процессоров в многопроцессорной системе.

Использование в современных быстродействующих вычислительных системах «магистрального» принципа выполнения команд и совмещения времени работы блоков оперативной памяти накладывает особые требования на структуру устройств управления оперативной памятью (УУОП).

В связи с необходимостью осуществления предварительной выборки команд и операндов УУОП содержат быстродействующие буферные регистры с ассоциативной выборкой, в которые заносится предварительно выбираемая из ОП информация, поступающая из равных одновременно работающих блоков ОП.

Известна вычислительная система [1], содержащая ряд центральных и периферийных процессоров и оперативную память, состоящую из нескольких блоков. В системе используется схема управления обращением к оперативной памяти, в которой каждый процессор должен постепенно отслеживать всю картину состояния всех блоков ОП что связано с дополнительными затратами оборудования и появлением дополнительных связей в системе и, кроме того, в системе всегда остается возможность конфликтных ситуаций с возможностью нескольких одновременных обращений к одному блоку ОП.

В подобной ситуации запрос, выставленный на входной регистр обращения К ОП в каждом процессоре, в общем случае должен храниться на нем до тех пор, пока из ОП не поступит сигнал о том, что, запрос принят в соответствующем блоке ОП и будет удовлетворен. При этом значительно снижается пропускная способность канала связи каждого процессора с ОП системы.

Из известных устройств наиболее близким по технической сущности к изобретению является устройство для управления обращением в оперативную память, которое содержит регистр обращения к памяти, узлы ответа, адресные регистры, а входы которых подключены к выходу коммутатора [2]

В таком устройстве применены счетчики цикла памяти, и очередное обращение не может поступить на выходной регистр, пока счетчик необходимого для него блока отсчитывает цикл, т.е. блок занят. Каждый новый запрос, поступивший на выходной регистр, занимает соответствующий блок ОП и запускает его счетчик цикла.

Адрес очередного обращения к ОП от одного из запросчиков: буфера операндов, буфера команд или буфера записи в соответствии с приоритетом и при условий свободы соответствующего блока ОП поступает на регистр обращения к ОП и с него на регистр адреса одного из блоков ОП. При этом запускается соответствующий этому блоку счетчик цикла, блокирующий обращение к данному блоку до конца его работы. Если имеются обращения к другим блокам ОП, которые в это время свободны, то они проходят на регистр обращения к ОП и с него на свои блоки, запуская соответствующие счетчики цикла. При такой организации всегда известно, по состоянию счетчиков, какие блоки ОП заняты, и адрес очередного обращения может поступить на регистр обращения только при условии свободы необходимого ему блока ОП. Поэтому, если адрес обращения поступил на регистр обращения, то обязательно через строго фиксированный промежуток времени запрос на обращение будет удовлетворен.

Однако подобное решение снижает пропускную способность канала связи процессора с ОП и степень использования оборудования оперативной памяти.

Целью изобретения является увеличение пропускной способности и повышение эффективности использования оборудования. Поставленная цель достигается тем, что в устройство введены блоки хранения очереди запросов, хранения таблицы занятости, приоритетного выбора запросов, формирования запросов, управления приемом запросов, дешифратор, узел сдвига, регистр выдачи, группы элементов И, элемент ИЛИ, причем первый выход регистра обращения к памяти подключен к первым входам первой группы элементов И, ко вторым входам которых подключены соответственно выходы элементов И второй группы, выходы элементов И первой группы соединены со входом блока хранения очереди запросов, первый выход которого через последовательно соединенные третью- группу элементов И, элемент ИЛИ и регистр выдачи подключен к входу коммутатора, второй выход блока хранения очереди запросов, подключен к -первому входу блока формирования запросов, второй вход которого соединен с выходом блока хранения таблицы занятости, а ВЫХОД подключен ко входу дешифратора и к первым входам узла сдвига и блока хранения Таблицы занятости, второй вход которого соединен с выходом узла сдвига, второй вход узла сдвига подключен к первому выходу блока управления приемом запросов, второй выход которого подключен к первым входам элементов И второй группы, вторые входы которых соединены соответственно с выходами блока приоритетного выбора запросов, а выходы — подключены к первым входам блока приоритетного выбора запросов и блока управления приемом запросов, вторые входы которых соединены соответственно со вторым выходом регистра обращения к памяти и с выходами узлов ответа, выход дешифратора соединен с соответствующими входами элементов И третьей группы.

Схема устройства представлена на чертеже, где обозначено: регистр обращения к памяти 1; адресные регистры 2, группа элементов И для выдачи кода адреса обращения в ОП 3 кабели связи процессора с ОП 4; группа элементов И для приема кода в буфер запросов 5; блок хранения очереди запросов 6; группа элементов И для приема на регистр выдачи 7; регистр выдачи 8; узлы ответа о приеме запроса на обслуживание в блок ОП 9; блок управления приемом запросов 10; блок приоритетного выбора запросов 11; группы разрядов 12 регистров блока 6, указывающие номер блока ОП, к которому должно быть обращение от данного запроса, блок формирования запроса 13; блок хранения таблицы занятости 14; узел сдвига 15; дешифратор 16, элемент ИЛИ 17; группа разрядов 18 регистра 1, характеризующая тип обращения к ОП; группа элементов И 19 для выработки сигнала управления приемом в регистры блока 6.

Работает устройство следующим образом.

Код адреса очередного запроса к ОП с регистра 1 поступает на один из регистров блока хранения очереди запросов 6. Определение регистра, на которой осуществляется прием очередного запроса, производится на основе анализа типа обращения, определяемого кодом группы разрядов регистра 1, состоянием блока 11 и состоянием блока 10. Запросы, принятые на регистры блока 6 поступают на блок 13, формирующий на основании приоритетов запросов и по состоянию блоков ОП занятым ранее данным процессором запрос к ОП, что определяется таблицей блока 14. Этот запрос через дешифратор 16, группу элементов И и элемент ИЛИ 17, подключает к регистру 8 один из регистров блока б хранения очереди запросов, определяемый блоком 13.

Одновременно устанавливают в «1» триггер занятости блока ОП, к которому адресован запрос, а номер блока ОП поступает на вход временного имитатора обращения к ОП, который связан со входами установки в «0» всех триггеров блока 14 хранения таблицы занятости.

Код на регистре 8 выдерживается минимальное время, необходимое для его приема в блок ОП при, условии его свободы, затем на регистр 8 выставляется следующий по приоритету запрос, сформированный блоком 13. Если через строго фиксированное время от блока ОП не поступает ответа о принятии запроса, выставленного на регистр 8, такой запрос считается неудовлетворительным, триггер занятости его блока, установленный ранее в «1», устанавливается узлом 15 в «0», запрос формируется снова блоком 13 и процесс повторяется. Если запрос на обращение принят блоком ОП, т.е. через фиксированное время после выдачи его на регистр 1 от блока ОП из узла 9 приходит подтверждение о его исполнении, то по истечении цикла ОП узел 15 осуществляет сброс триггера таблицы блока 14, соответствующего данному блоку ОП. Кроме того, по сигналу от узла 9 через блок 10 осуществляется освобождение регистра блока 6, обращение которого находится в стадии исполнения блоком ОП. Таким образом, каждое обращение, периодически поступает на кодовые шины обращения к ОП, занимая их и регистр 8 на короткое время, до тех пор, пока нё окажется свободным блок ОП.

Формула изобретения

Устройство для управления обращением в оперативную память, содержащее регистр обращения к памяти, узлы ответа, адресные регистры, входы которых подключены к выходу коммутатора, отличающееся тем, что, с целью увеличения пропускной способности и повышения эффективности использования оборудования, в него введены блоки хранения очереди запросов, хранения таблицы занятости, приоритетного выбора запросов, формирования запросов, управления приемом запросов, дешифратор, узел сдвига, регистр выдачи, группы элементов И, элемент ИЛИ, причем первый выход регистра обращения к памяти подключен к первым входам первой группы элементов И, ко вторым входам которых подключены соответственно выходы элементов И второй группы, выходы элементов И первой группы соединены со входами блока хранения очереди запросов, первый выход которого через последовательно соединенные третью группу элементов И, элемент ИЛИ и регистр выдачи подключен ко входу коммутатора, второй выход блока хранения очереди запросов подключен к первому входу блока формирования запросов, второй вход которого соединен с выходом блока хранения таблицы занятости, а выход подключен ко входу дешифратора и к первым входам узла сдвига и блока хранения таблицы занятости, второй вход которого соединен с выходом узла сдвига, второй вход узла сдвига подключен к первому выходу блока управления приемом запросов, второй выход которого подключен к первым входам элементов И второй группы, вторые входы которых соединены соответственно с выходами блока приоритетного выбора запросов, а выходы подключены к первым входам блока приоритетного выбора запроса и блока управления приемом запросов, вторые входы которых соединены соответственно со вторым выходом регистра обращения к памяти и с выходами узлов ответа, выход дешифратора соединен с соответствующими входами элементов И третьей группы.

Источники информации, принятые во внимание при экспертизе

- Патент США 3905023, кл. 340—172.6, 235-153 АР, кл. G06 F11/06; G06 F15/16, 1975.

- Королев Л, Н. Структуры ЭВМ и их математическое обеспечение, М., «Наука», 1974, с. 72—76.

Материал помещен в музей 21.08.2009 года