A-50 Computer

Home → Articles → A-50 Computer

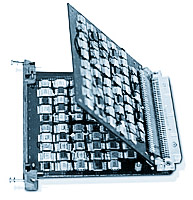

- A-50 airborne computer.

- Chief designer: V. I. Shteinberg. Development engineers: V. I. Monakhov, M. A. Tereshchenko, V. I. Tuzhilin, V. I. Alekseyev, V. B. Ivanov, V. N. Kartavets, Yu. Kh. Kleiman, A. A. Kriksin, Yu. R. Lemzal, A. A. Makarov, A. S. Salman.

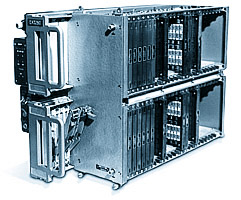

A-40/A-50 universal unit

- Designing organization: Research Institute of Computer Engineering (NICEVT) of the USSR Ministry of Radio Engineering (since 1986 - Research Institute NII Argon).

- Manufacturer: Astrakhan Progress factory, Brest electromechanical factory.

- Completion of development: 1985.

- Beginning of production: 1986.

- Termination of production: still in production.

- Field of application: automated control systems of military installations.

- Number of machines produced: over 1,000.

- Description: A-50 is a high-end model of unified high-performance 32-bit airborne computers based on the ES EVM architecture. It uses circuitry, design and technological solutions developed for A-40 machine. At the same time the creation of new element base allowed one to sharply increase its performance, RAM capacity and the number of I/O channels. Two A-50 computers can be clustered with direct control. The computer contains a control console with serial interface; its CPU has a cache and a microtest system. A tape drive and bubble memory qualified for using in severe conditions and also service equipment including a subscriber simulation console and a service computer are specially developed.

A-50 computer

To increase the processor speed, the instruction unit circuitry is optimized, which corrects dependent commands. A-50 is controlled by firmware including functional microcodes and microtests for troubleshooting with a resolution up to a single cell. RAM and firmware contain double-error detecting and single-error correcting codes. An ingenious structure of cache contains command and data buffers. The structure of I/O channels provides relatively high throughput in minimal hardware configuration, and their interaction is organized so that the I/O subsystem moderately reduces the CPU performance.

A-50 computer has become the basis for eight modifications of single- and two-computer systems developed in the framework of top-priority state programs. The design of A-50 makes it a basic machine suitable for using in aircraft, mobile and stationary installations.

Instruction set - full ES EVM-1 set plus sine, cosine and inverse calculation commands.

Data types - byte, 16-bit word, 32-bit double word.

Instruction word length - 16 and 32 bits.

Interrupt system - multilevel.

Machine cycle - 250 ns.

Speed - 2,000,000 operations per second in format RR.

Performance - 540,000 operations per second with Gibson 3E mixture.

Cache capacity - 4 Kbytes.

RAM - 565RU5 LSI-based; access time - 120 to 250 ns; capacity - 4 or 16 Mbytes.

Firmware capacity - 272 Kbytes.

Number of I/O channels - 4.

Total I/O channels throughput: 4 Mbps in burst mode; 600 Kbps in byte-multiplex mode.

External ROM: capacity - 2x512 Kbytes; reading speed - 500 Kbps; max. data storage time - 1,000 h.

Tape drive (chief designer V. S. Klepinin): capacity - 4x2 Mbytes; average access time - 60 s; throughput - 15 Kpbs.

Bubble memory (chief designer R. V. Smirnov): capacity - 2x2 Mbytes; access time - 7 ms; writing time - 100 s; throughput - 40 Kbps.

- Element base: 134, 136, 130 and 133 series MSIs.

- Design: modular with three hierarchical levels - a cell, a unit and a cabinet. A cell consists of two multilayer printed circuit boards electrically connected by wires or printed stubs and equipped with a 135-pin connector. The cells comprise a functionally and technically accomplished unit and are interconnected through special terminal blocks which fasten the connector plugs to the frame and provide 0- and 5-V circuit organization through a bus system. Wire wrap method is used for cell switching. The units are mechanically attached to a chassis and electrically connected by wires. The design of computer units and bodies is ingenious, with two-board cells providing a higher component density. CPU, RAM, I/O and power supply units are installed in a common body (cabinet) while a control console is designed as a separate stand-alone unit. The machine is equipped with forced air-cooling system.

- Technology: ES EVM-like unified multilayer printed circuit boards manufactured by metal coating of through holes. The number of switching layers is up to 10.

- Software: custom real-time operating system, automated programming and debugging systems, service programs and test check programs.

- Specifications:

Vibratory load - up to 5 g at a frequency range from 0 to 2,000 Hz.

Single impacts - up to 20 g.

Relative humidity - up to 98%.

The lowest air pressure - 200 mm Hg.

Range of operating temperatures - from -10 to +50°C.

Size of a processor - 640x620x581 mm.

Size of a control console - 680x483x391 mm.

Weight - 140 kg.

Power consumption - 1,000 W.

MTBF - 800 h.

Recovery time - 30 min.

- Special features: the most high-performance domestic computer of late 80s and early 90s. The first airborne computer conforming to the requirements for aviation, mobile and stationary installations.