Устройство памяти гипотез ЭВМ М-13

Н.В. Георгиев, А.А. Крупский, Ю.Б. Левин

Рассмотрено устройство памяти гипотез, входящее в состав процессора обработки функций ЭВМ М-1З в качестве его локальной памяти. Описанные технические решения устройства учитывают особенности выполнения алгоритмов процессора и позволяют обеспечить его высокую производительность.

Устройство памяти гипотез (УПГ) предназначено к использованию в процессоре обработки функций (ПОФ) ЭВМ М-1З, рассчитанном на выполнение узкого фиксированного набора процедур с максимальной эффективностью. С точки зрения системы памяти машины М-1З в целом, устройство УПГ, представляющее собой специализированное многопортовое ЗУ с разрешением конфликтов при обращении, служит локальной памятью процессора обработки функций. Наименование “устройство памяти гипотез” устройство УПГ получило в связи с тем, что основным назначением ПОФ является реализация быстрого преобразования Фурье.

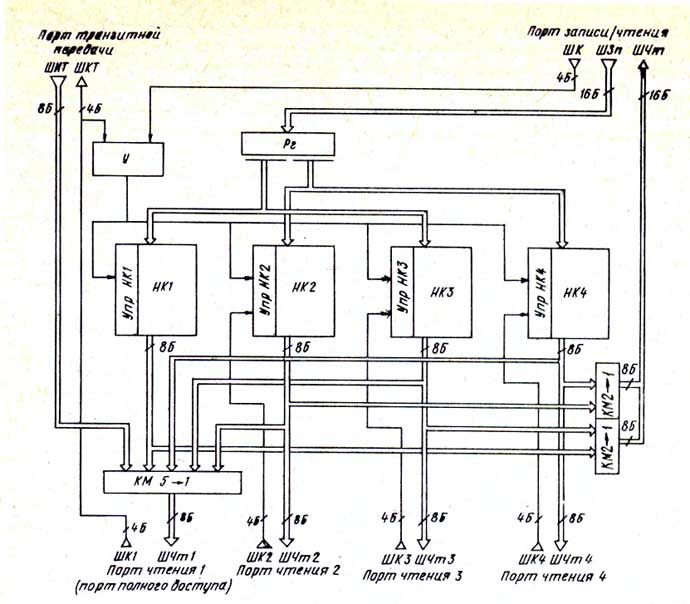

Одним из путей обеспечения эффективности ПОФ является учет структуры обрабатываемой информации и особенностей выполняемых процедур в функциональных свойствах и интерфейсах УПГ. Информация, подлежащая обработке, поступает в систему ПОФ из главной памяти М-1З и возвращается в главную память по завершении обработки. Структурная схема устройства представлена на рисунке, где ШЧт, ШЗп, ШК — шины чтения, записи и командная универсального порта; ШЧт1 — ШЧт4, ШК1 — ШК4 — шины чтения и командные шины портов чтения; ШИТ, ШКТ — информационная и командная шины порта транзитной передачи. Форматы шин на рисунке обозначены в байтах.

Устройство УПГ имеет емкость 4 Мбайт и реализовано на динамических БИС памяти n МОП типа 565РУЗ (16 Кбит). Всего в системе ПОФ предусмотрено подключение до 10 устройств УПГ емкостью до 40 Мбайт. За счет интерливинга 4:1 такт обращения к устройству составляет 300 нс.

Устройство УПГ оснащено пятью портами, один из которых универсальный на запись/чтение и служит для загрузки информации в УПГ из главной памяти, либо из процессорных устройств ПОФ, а также выгрузки информации из УПГ в обратном направлении. Остальные четыре порта — порты чтения, которые служат для выборки из устройства УГIГ различных составляющих информации и передачи этих составляющих в процессорные устройства ПОФ в качестве управляющей информации.

Структурная схема устройства УПГ

Со стороны порта записи/чтения устройство функционирует с форматом обращения 16 байт и адресностью 256 К. Со стороны портов чтения устройство представляет собой четыре независимых ЗУ, емкость каждого из них — 1 Мбайт. Это достигнуто путем закрепления за каждым портом чтения фиксированной области памяти. На рисунке эти области памяти показаны как отдельные накопители НК1 — НК4, имеющие свои узлы управления УпрНК1-УпрНК4. Интерфейс обмена порта чтения предусматривает форматы обращения 8, 4 и 2 байта при адресности соответственно 128, 256 и 512К. Возможность хранения и выдачи информации в различных форматах позволяет использовать емкость устройства с наибольшей эффективностью за счет максимально плотного расположения этой информации в разрядной сетке.

Функции контроллера универсального порта и порта полного доступа выполняет центральный узел управления устройством (УУпр). Назначение показанных на рисунке коммутаторов (КМ), обслуживающих шины чтения универсального порта и порта полного доступа, а также регистра (Рг), подключенного к шине записи универсального порта, понятно из схемы и дополнительных пояснений не требует.

В устройстве УПГ предусмотрены две модификации режима чтения. В обычном режиме каждая прочитанная строка фиксируется на выходных шинах в течение одного такта, в модифицированных режимах — в течение двух или четырех тактов. Это техническое решение позволило существенно сэкономить общий объем аппаратуры ПОФ, поскольку в УПГ оно обходится практически без дополнительного оборудования, а перенесение функции задержки в процессорные устройства ПОФ потребовало бы большого числа громоздких регистров. Одновременно интерфейс порта чтения предусматривает два варианта размещения информации форматом 4 байта на 8-байтвой выходной шине порта: информация может размещаться либо в старших, либо в младших байтах шины.

Один из четырех портов чтения (порт полного доступа) обеспечивает возможность обращения ко всей памяти (4 Мбайт) устройства. Кроме того, как отмечалось выше, в ПОФ обеспечена возможность расширения емкости памяти путем подключения в систему нескольких устройств УПГ; при этом разные устройства или группы устройств УПГ могут реализовать разные функции, как-то: прием, хранение и выдача массивов, подлежащих обработке, и промежуточных результатов обработки, либо прием, хранение и выдача управляющей информации, необходимой для работы процессорных устройств. Замена последней происходит сравнительно редко.

Увеличенная за счет объединения двух или нескольких устройств УПГ емкость памяти доступна по чтению для абонента, подключенного к порту полного доступа. С целью реализации указанного объединения в устройстве предусмотрен порт транзитной передачи. Он соединяется с портом полного доступа того устройства, с которым производится объединение, и осуществляет передачу поступающей на его вход информации на выходную шину порта полного доступа своего устройства. При объединении с третьим устройством оно подключается, аналогично описанному, ко второму устройству и т. д.

Для универсального порта чтения/записи, для портов чтения и порта транзитной передачи предусмотрены информационные (входные и выходные) и командные шины.

По командным шинам в устройство поступают командные слова, содержащие указания о величине и расположении информационного массива, подлежащего передаче, формате выдаваемых данных, модификациях режимов. Алгоритм взаимодействия по командным шинам различен для различных портов. Интерфейс универсального порта рассчитан на асинхронную передачу кванта управляющей информации с квитированием. Полный объем управляющей информации передается за 7 тактов обмена. После этого в устройство поступает команда, инициирующая исполнение заданного обмена. По командным шинам порта чтения управляющая информация поступает синхронно в виде двух посылок. Исполнение заданного обмена происходит, безусловно, после получения управляющей информации. Таким образом, каждый порт устройства в пределах реализуемого им интерфейса является программно управляемым, а специализация портов осуществлена аппаратно. Такой подход более целесообразен и экономичен, чем использование для всех случаев унифицированного порта, рассчитанного на реализацию любого интерфейса, применяемого в системе.

Заключение. Устройство памяти гипотез обеспечивает необходимую аппаратную поддержку высокой (порядка миллиардов операций в секунду) производительности процессора обработки функций М-1З благодаря максимальному учету в структуре памяти особенностей выполнения всех алгоритмов ПОФ. При этом на устройство УПГ возложено выполнение вспомогательных функций ПОФ — промежуточное хранение информации, ее сдвиг и “упаковка” в разрядной сетке и др., что позволяет освободить от этих функций основное процессорное оборудование ПОФ.

Принятые при разработке УПГ технические решения позволили ограничиться в системе ПОФ одним универсальным устройством памяти и тем самым сократить номенклатуру устройств ПОФ.

Статьи об ЭВМ М-13

Сборник “Вопросы радиоэлектроники”, серия “Электронная вычислительная техника”, выпуск 10, 1990 г.

Перепечатывается с разрешения авторов.

Статья помещена в музей 22.02.2007 г.